FEATURES

► Einzelne 8-, 10-, 12-Bit-DACs, 2 LSB INL

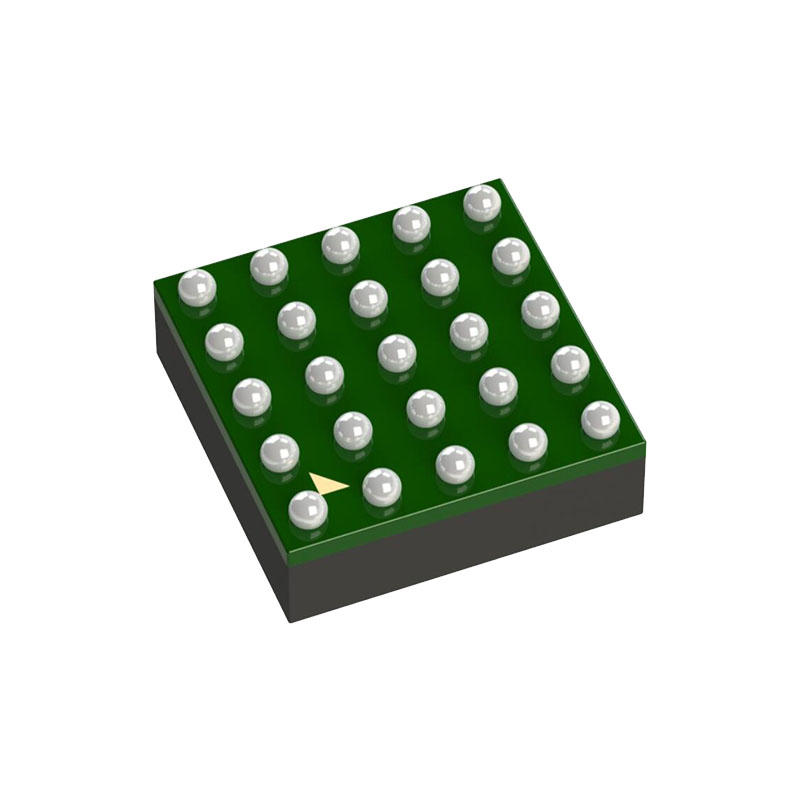

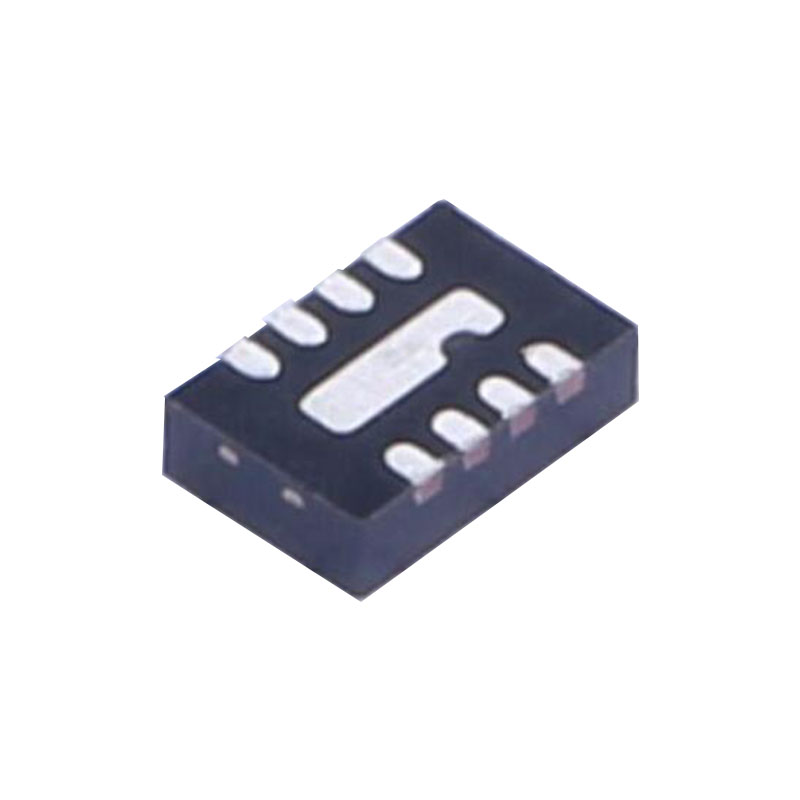

► 6-polige LFCSP- und SC70-Gehäuse

► Micropower-Betrieb: 100 µA maximal bei 5 V

► Stromsparend bis <150 nA bei 3 V

► 2,7 V bis 5,5 V Spannungsversorgung

► Garantiert monoton durch Design

► Power-on-Reset auf 0 V mit Brownout-Erkennung

► 3 Ausschaltfunktionen

► I2C-kompatible serielle Schnittstelle unterstützt die Modi Standard (100 kHz), Schnell (400 kHz) und Hochgeschwindigkeit (3,4 MHz)

► On-Chip-Ausgangspufferverstärker, Rail-to-Rail-Betrieb

► AEC-Q100 qualifiziert für Automobilanwendungen

ANWENDUNGEN

► Prozesskontrolle

► Datenerfassungssysteme

► Tragbare, batteriebetriebene Instrumente

► Digitale Verstärkung und Offset-Anpassung

► Programmierbare Spannungs- und Stromquellen

► Programmierbare Dämpfungsglieder

ALLGEMEINE BESCHREIBUNG

Die AD5602/AD5612/AD5622, Mitglieder der nanoDAC®-Familie, sind gepufferte 8-, 10- und 12-Bit-Digital-Analog-Wandler (DAC) mit Spannungsausgang, die mit einer einzigen 2,7-V- bis 5,5-V-Versorgung arbeiten und nur

Die AD5602/AD5612/AD5622 verwenden eine 2-Draht I2C kompatible serielle Schnittstelle, die in den Modi Standard (100 kHz), Schnell (400 kHz) und Hochgeschwindigkeit (3,4 MHz) arbeitet.

Die Referenzen für AD5602/AD5612/AD5622 werden von den Stromversorgungseingängen abgeleitet, um einen möglichst großen dynamischen Ausgangsbereich zu erhalten. Jeder Baustein verfügt über einen Power-On-Reset-Schaltkreis, der sicherstellt, dass der DAC-Ausgang auf 0 V hochgefahren wird und dort verbleibt, bis ein gültiger Schreibvorgang in den Baustein erfolgt. Die Bausteine enthalten eine Power-Down-Funktion, die den Stromverbrauch der Bausteine auf <150 nA bei 3 V reduziert und per Software wählbare Ausgangslasten im Power-Down-Modus bereitstellt. Die Bausteine werden über die serielle Schnittstelle in den Power-Down-Modus versetzt. Der geringe Stromverbrauch der AD5602/AD5612/AD5622 im Normalbetrieb macht sie ideal für den Einsatz in tragbaren, batteriebetriebenen Geräten geeignet. Die typische Leistungsaufnahme beträgt 0,4 mW bei 5 V.

PRODUKT-HIGHLIGHTS

- Erhältlich in 6-poligen LFCSP- und SC70-Gehäusen.

- Maximaler Stromverbrauch von 100 µA, Betrieb mit einer einzigen Versorgungsspannung: Diese Bausteine arbeiten mit einer einzigen Versorgungsspannung von 2,7 V bis 5,5 V und verbrauchen typischerweise 0,2 mW bei 3 V und 0,4 mW bei 5 V, was sie ideal für batteriebetriebene Anwendungen macht.

- Der On-Chip-Ausgangspufferverstärker ermöglicht es, dass der Ausgang des DAC von Schiene zu Schiene mit einer typischen Anstiegsrate von 0,5 V/µs schwingt.

- Von der Stromversorgung abgeleitete Referenz.

- I2C-Schnittstelle im Standard-, Schnell- und Hochgeschwindigkeitsmodus.

- Entwickelt für einen sehr niedrigen Stromverbrauch.

- Fähigkeit zum Herunterfahren. Im ausgeschalteten Zustand verbraucht der DAC typischerweise <150 nA bei 3 V.

- Power-on-Reset und Brownout-Erkennung.

SERIELLE SCHNITTSTELLE

Die AD5602/AD5612/AD5622 haben 2-Draht I2C-kompatible serielle Schnittstellen. Der AD5602/AD5612/AD5622 kann als Zielgerät an einen I2C-Bus angeschlossen werden, unter der Kontrolle eines Controller-Geräts.

Die AD5602/AD5612/AD5622 unterstützen die Datenübertragungsmodi Standard (100 kHz), Schnell (400 kHz) und Hochgeschwindigkeit (3,4 MHz). Die 10-Bit-Adressierung und die allgemeine Call-Adressierung werden nicht unterstützt.

Der AD5602/AD5612/AD5622 hat jeweils eine 7-Bit-Zieladresse. Die fünf höchstwertigen Bits (MSB) sind 00011 und die beiden LSBs werden durch den Zustand des ADDR-Pins bestimmt. Durch die Möglichkeit, ADDR per Festverdrahtung zu ändern, kann der Benutzer bis zu drei dieser Geräte in einen Bus einbinden.

Das 2-drahtige serielle Busprotokoll funktioniert wie folgt:

- Der Controller leitet die Datenübertragung ein, indem er eine Startbedingung herstellt. Dies ist der Fall, wenn ein Übergang von High zu Low auf der SDA-Leitung erfolgt, während SCL High ist. Das folgende Byte ist das Adressbyte, das aus der 7-Bit-Zieladresse besteht. Die Zieladresse, die der übertragenen Adresse entspricht, antwortet, indem sie SDA während des neunten Taktimpulses auf low zieht (dies wird als Acknowledge-Bit bezeichnet). In dieser Phase bleiben alle anderen Geräte auf dem Bus im Leerlauf, während das ausgewählte Gerät darauf wartet, dass Daten in sein Schieberegister geschrieben oder daraus gelesen werden.

- Daten werden über den seriellen Bus in Sequenzen von neun Takten übertragen (acht Datenbits gefolgt von einem Bestätigungsbit). Die Übergänge auf der SDA-Leitung müssen während der Low-Periode von SCL erfolgen und während der High-Periode von SCL stabil bleiben.

- Wenn alle Datenbits gelesen oder geschrieben wurden, wird ein Stoppzustand hergestellt. Im Schreibmodus zieht der Controller während des 10. Takts die SDA-Leitung auf High, um eine Stop-Bedingung herzustellen. Wenn eine Stop-Bedingung zwischen dem 7. und 8. Takt des I2C-Adressrahmens erzeugt wird, ist ein Stromzyklus erforderlich, um das Gerät wiederherzustellen. Im Lesemodus gibt der Controller beim neunten Taktimpuls eine Nichtbestätigung aus (d.h. die SDA-Leitung bleibt auf High). Der Controller setzt dann die SDA-Leitung vor dem 10. Taktimpuls auf Low und während des 10. Taktimpulses auf High, um einen Stoppzustand herzustellen.