ALLGEMEINE BESCHREIBUNG

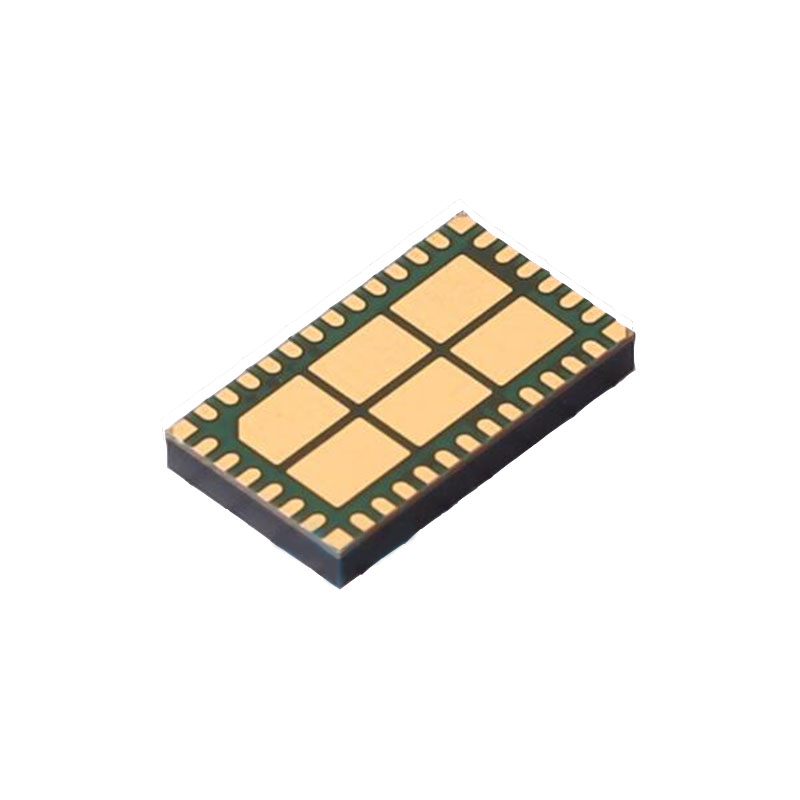

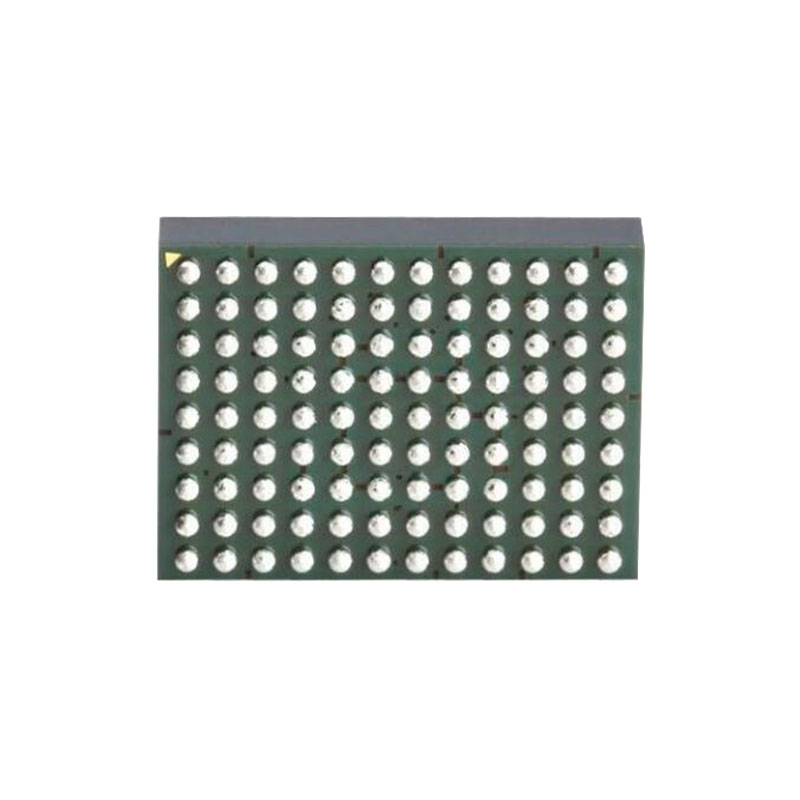

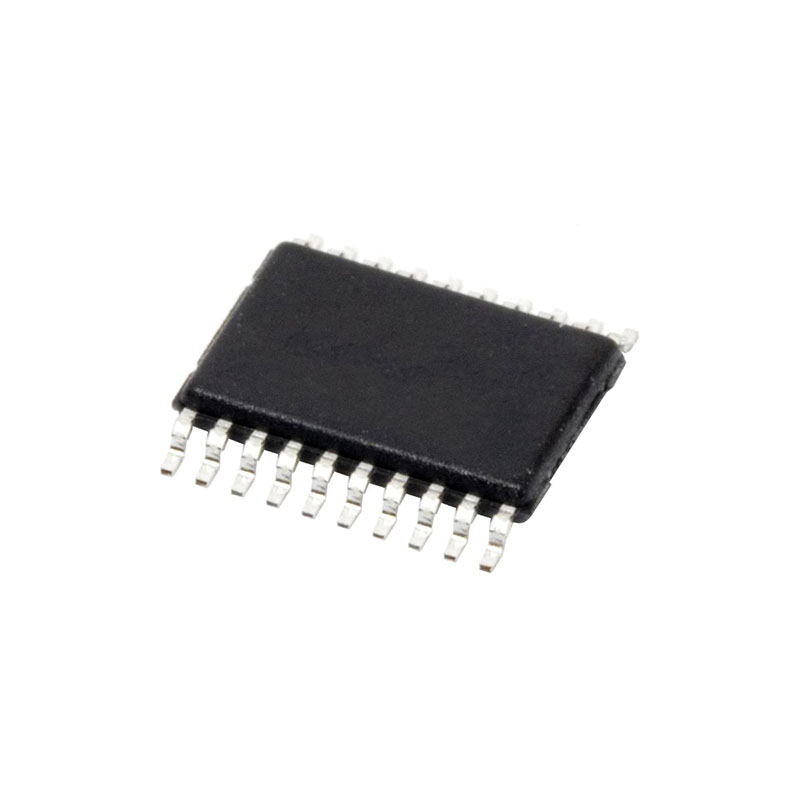

Der AD9634 ist ein 12-Bit-Analog-Digital-Wandler (ADC) mit einer Abtastgeschwindigkeit von bis zu 250 MSPS. Der AD9634 wurde zur Unterstützung von Kommunikationsanwendungen entwickelt, bei denen niedrige Kosten, geringe Größe, große Bandbreite und Vielseitigkeit gefragt sind. Der ADC-Kern verfügt über eine mehrstufige, differenzielle Pipeline-Architektur mit integrierter Ausgangskorrekturlogik. Der ADC verfügt über Eingänge mit großer Bandbreite, die eine Vielzahl von vom Benutzer auswählbaren Eingangsbereichen unterstützen können. Eine integrierte Spannungsreferenz erleichtert die Designüberlegungen. Ein Duty-Cycle-Stabilisator (DCS) kompensiert Schwankungen im ADC-Taktzyklus, so dass der Wandler eine hervorragende Leistung beibehält. Die ADC-Ausgangsdaten werden direkt an den externen 12-Bit-LVDS-Ausgangsport weitergeleitet. Die Programmierung für Setup und Steuerung erfolgt über eine 3-Draht SPI-kompatible serielle Schnittstelle. Der AD9634 ist in einem 32-poligen LFCSP-Gehäuse erhältlich und für den industriellen Temperaturbereich von -40°C bis +85°C spezifiziert. Dieses Produkt ist durch ein U.S.-Patent geschützt.

PRODUKT-HIGHLIGHTS

- Integrierter 12-bit, 170 MSPS/210 MSPS/250 MSPS ADC.

- Schnelle Erkennung von Bereichsüberschreitungen und Schwellenwerten.

- Der proprietäre Differenzeingang sorgt für eine hervorragende SNR-Leistung bei Eingangsfrequenzen von bis zu 350 MHz.

- 3-poliger, 1,8 V SPI-Port für die Programmierung und das Auslesen von Registern.

- Pin-Kompatibilität mit dem AD9642, was eine einfache Migration auf bis zu 14 Bit ermöglicht, und mit dem AD6672.

FEATURES

SNR = 69,7 dBFS bei 185 MHz AIN und 250 MSPS

SFDR = 87 dBc bei 185 MHz AIN und 250 MSPS

-150,6 dBFS/Hz Eingangsrauschen bei 185 MHz, -1 dBFS AIN und 250 MSPS

Gesamtleistungsaufnahme: 360 mW bei 250 MSPS

1,8 V Versorgungsspannungen

LVDS-Ausgänge (ANSI-644-Pegel)

Ganzzahliger 1-zu-8 Eingangstaktteiler (625 MHz maximaler Eingang)

Abtastraten von bis zu 250 MSPS

Interne ADC-Spannungsreferenz

Flexibler Analogeingangsbereich 1,4 V p-p bis 2,0 V p-p (1,75 V p-p nominal)

ADC-Takt-Tastverhältnis-Stabilisator

Steuerung der seriellen Schnittstelle

Energiesparende Abschaltmodi

ANWENDUNGEN

Kommunikation

Diversity-Funksysteme

Digitale Multimode-Empfänger (3G) TD-SCDMA, WiMAX, W-CDMA, CDMA2000, GSM, EDGE, LTE

I/Q-Demodulationssysteme

Intelligente Antennensysteme

Mehrzweck-Software-Radios

Ultraschallgeräte

Breitband-Datenanwendungen

ARBEITSTHEORIE

Der AD9634 kann mit Hilfe einer geeigneten Tiefpass- oder Bandpassfilterung an den ADC-Eingängen jedes beliebige fS/2-Frequenzsegment von DC bis 250 MHz mit geringem Verlust an ADC-Leistung abtasten. Die Programmierung und Steuerung des AD9634 erfolgt über eine 3-polige, SPI-kompatible serielle Schnittstelle.

ADC-ARCHITEKTUR

Die Architektur des AD9634 besteht aus einer Front-End-Sample-and-Hold-Schaltung, gefolgt von einem Pipeline-ADC mit geschalteten Kondensatoren. Die quantisierten Ausgänge jeder Stufe werden in der digitalen Korrekturlogik zu einem endgültigen 12-Bit-Ergebnis kombiniert. Die Pipeline-Architektur ermöglicht es, dass die erste Stufe mit einem neuen Eingangsabtastwert arbeitet und die übrigen Stufen mit den vorhergehenden Abtastwerten arbeiten. Die Abtastung erfolgt mit der steigenden Flanke des Taktgebers. Jede Stufe der Pipeline, mit Ausnahme der letzten, besteht aus einem Flash-ADC mit niedriger Auflösung, der mit einem Digital-Analog-Wandler (DAC) mit geschaltetem Kondensator und einem Zwischenstufen-Rückstandsverstärker (MDAC) verbunden ist. Der MDAC vergrößert die Differenz zwischen dem rekonstruierten DAC-Ausgang und dem Flash-Eingang für die nächste Stufe in der Pipeline. In jeder Stufe wird ein Bit Redundanz verwendet, um die digitale Korrektur von Flash-Fehlern zu erleichtern. Die letzte Stufe besteht einfach aus einem Flash-ADC. Die Eingangsstufe enthält eine differentielle Abtastschaltung, die im differentiellen oder unsymmetrischen Modus ac- oder dc-gekoppelt sein kann. Der Output Staging Block richtet die Daten aus, korrigiert Fehler und gibt die Daten an die Ausgangspuffer weiter. Die Ausgangspuffer werden von einer separaten Versorgung gespeist, so dass das digitale Ausgangsrauschen vom analogen Kern getrennt werden kann. Beim Herunterfahren gehen die Ausgangspuffer in einen hochohmigen Zustand über.

Weitere Parameter entnehmen Sie bitte den Datenblättern.