ALLGEMEINE BESCHREIBUNG

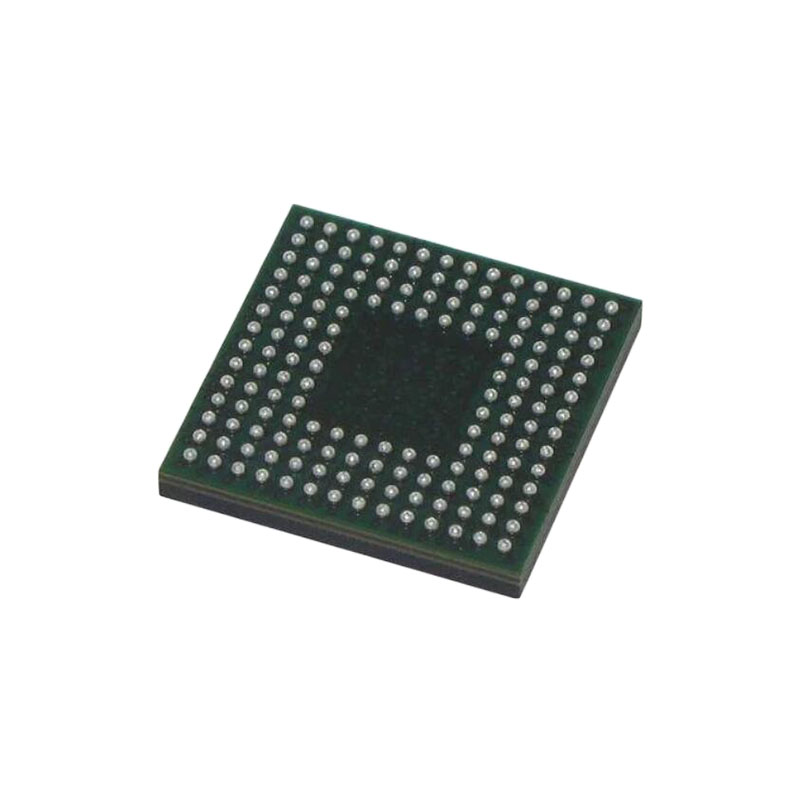

The AD9642 is a 14-bit analog-to-digital converter (ADC) with sampling speeds of up to 250 MSPS. The AD9642 is designed to support communications applications, where low cost, small size, wide bandwidth, and versatility are desired. The ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. The ADC features wide bandwidth inputs that can support a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer (DCS) is provided to compensate for variations in the ADC clock duty cycle, allowing the converter to maintain excellent performance. The ADC output data is routed directly to the external 14-bit LVDS output port. Flexible power-down options allow significant power savings, when desired. Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface. The AD9642 is available in a 32-lead LFCSP and is specified over the industrial temperature range of −40°C to +85°C. This product is protected by a U.S. patent.

PRODUKT-HIGHLIGHTS

Integrated 14-bit, 170 MSPS/210 MSPS/250 MSPS ADC.

Operation from a single 1.8 V supply and a separate digital output driver supply accommodating LVDS outputs.

Der proprietäre Differenzeingang sorgt für eine hervorragende SNR-Leistung bei Eingangsfrequenzen von bis zu 350 MHz.

3-poliger, 1,8 V SPI-Port für die Programmierung und das Auslesen von Registern.

Pin compatibility with the AD9634, allowing a simple migration from 14 bits to 12 bits, and with the AD6672.

FEATURES

SNR = 71.0 dBFS at 185 MHz AIN and 250 MSPS

SFDR = 83 dBc at 185 MHz AIN and 250 MSPS

−152.0 dBFS/Hz input noise at 200 MHz, −1 dBFS AIN, 250 MSPS

Total power consumption: 390 mW at 250 MSPS

1,8 V Versorgungsspannungen

LVDS-Ausgänge (ANSI-644-Pegel)

Ganzzahliger 1-zu-8 Eingangstaktteiler (625 MHz maximaler Eingang)

Abtastraten von bis zu 250 MSPS

Interne ADC-Spannungsreferenz

Flexibler Analogeingangsbereich 1,4 V p-p bis 2,0 V p-p (1,75 V p-p nominal)

ADC-Takt-Tastverhältnis-Stabilisator

Steuerung der seriellen Schnittstelle

Energy saving power-down modes

ANWENDUNGEN

Kommunikation

Diversity-Funksysteme

Multimode digital receivers (3G)

TD-SCDMA, WiMAX, WCDMA,

CDMA2000, GSM, EDGE, LTE

I/Q-Demodulationssysteme

Intelligente Antennensysteme

Mehrzweck-Software-Radios

Ultraschallgeräte

Breitband-Datenanwendungen

ANWENDUNGSINFORMATIONEN

DESIGN GUIDELINES

Before starting system level design and layout of the AD9642, it is recommended that the designer become familiar with these guidelines, which discuss the special circuit connections and layout requirements for certain pins.

Power and Ground Recommendations

When connecting power to the AD9642, it is recommended that two separate 1.8 V supplies be used: use one supply for analog (AVDD) and a separate supply for the digital outputs (DRVDD). The designer can employ several different decoupling capacitors to cover both high and low frequencies. Locate these capacitors close to the point of entry at the PC board level and close to the pins of the part with minimal trace length. A single PCB ground plane should be sufficient when using the AD9642. With proper decoupling and smart partitioning of the PCB analog, digital, and clock sections, optimum performance can be easily achieved.

VCM

Decouple the VCM pin to ground with a 0.1 μF capacitor, as shown in Figure 48.

SPI Port

The SPI port should not be active during periods when the full dynamic performance of the converter is required. Because the SCLK, CSB, and SDIO signals are typically asynchronous to the ADC clock, noise from these signals can degrade converter performance. If the on-board SPI bus is used for other devices, it may be necessary to provide buffers between this bus and the AD9642 to keep these signals from transitioning at the converter input pins during critical sampling periods.