DESCRIPCIÓN GENERAL

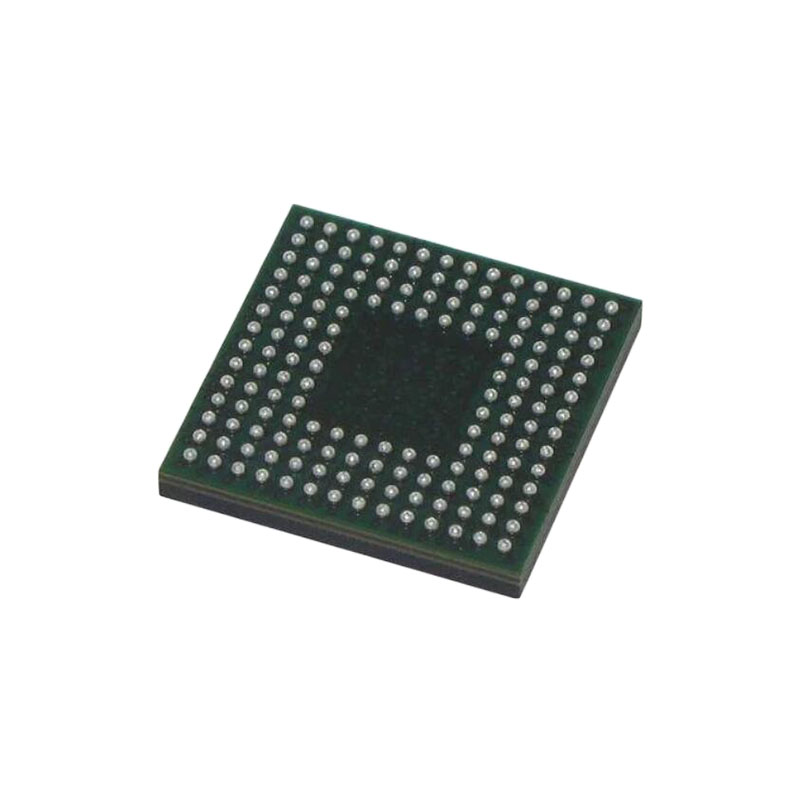

Los AD9736, AD9735 y AD9734 son DAC de alto rendimiento y alta frecuencia que proporcionan frecuencias de muestreo de hasta 1200 MSPS, permitiendo la generación de multiportadoras hasta su frecuencia de Nyquist. El AD9736 es el miembro de 14 bits de la familia, mientras que el AD9735 y el AD9734 son los miembros de 12 y 10 bits, respectivamente. Incluyen un puerto de interfaz periférica serie (SPI) que permite programar muchos parámetros internos y leer los registros de estado. Para alcanzar la alta frecuencia de muestreo se utiliza una interfaz LVDS de especificación reducida. La corriente de salida puede programarse en un rango de 8,66 mA a 31,66 mA. La familia AD973x se fabrica en un proceso CMOS de 0,18 µm y funciona con alimentaciones de 1,8 V y 3,3 V para un consumo total de 380 mW en modo bypass. Se suministra en una matriz de rejilla esférica a escala de chip de 160 terminales para reducir las parásitas del paquete.

PRODUCTOS DESTACADOS

1.Las características de bajo ruido y distorsión por intermodulación (IMD) permiten una síntesis de alta calidad de señales de banda ancha a frecuencias intermedias de hasta 600 MHz.

2.Los receptores de datos LVDS de doble velocidad de transmisión de datos (DDR) admiten una velocidad de conversión máxima de 1200 MSPS.

3.La programabilidad directa de los pines de las funciones básicas o el acceso al puerto SPI ofrecen un control completo de todas las funciones de la familia AD973x.

4.Fabricada en un proceso CMOS, la familia AD973x utiliza una técnica de conmutación propia que mejora el rendimiento dinámico.

5.La(s) salida(s) de corriente de la familia AD9736 se configuran fácilmente para topologías de circuito monotérmino o diferencial.

CARACTERÍSTICAS

Familia compatible con clavijas

Excelente rendimiento dinámico

AD9736: SFDR = 82 dBc a fOUT = 30 MHz

AD9736: SFDR = 69 dBc a fOUT = 130 MHz

AD9736: IMD = 87 dBc a fOUT = 30 MHz

AD9736: IMD = 82 dBc a fOUT = 130 MHz

Interfaz de datos LVDS con terminaciones de 100 Ω en chip

Autocomprobación integrada Integridad de muestreo LVDS Integridad de transferencia de datos LVDS a DAC

Bajo consumo: 380 mW (IFS = 20 mA; fOUT = 330 MHz)

Funcionamiento con doble alimentación 1,8/3,3 V

Salida analógica ajustable de 8,66 mA a 31,66 mA (RL = 25 Ω a 50 Ω)

Referencia en chip de 1,2 V

Encapsulado CSP_BGA (chip scale ball grid array) de 160 terminales

APLICACIONES

Sistemas de comunicaciones de banda ancha Infraestructura celular (predistorsión digital) CMTS/VOD inalámbricos punto a punto

Instrumentación, equipos automáticos de ensayo

Radar, aviónica

TEORÍA DE FUNCIONAMIENTO

Los AD9736, AD9735 y AD9734 son DAC de 14, 12 y 10 bits que funcionan a una velocidad de actualización de hasta 1,2 GSPS. Los datos de entrada se pueden aceptar hasta la tasa completa de 1,2 GSPS, o se puede habilitar un filtro de interpolación 2× (modo 2×) que permite el funcionamiento a máxima velocidad con una tasa de datos de entrada de 600 MSPS. Las entradas DATA y DATACLK_IN son LVDS paralelas, cumpliendo las especificaciones LVDS de oscilación reducida del IEEE con la excepción de la histéresis de entrada. La entrada DATACLK_IN funciona a la mitad de la velocidad de entrada DATA en un formato de doble velocidad de datos (DDR). Las entradas DACCLK-/DACCLK+ (Pin E1 y Pin F1) controlan directamente el núcleo DAC para minimizar el jitter del reloj. La señal DACCLK también se divide por 2 (modo 1× y 2×) y se emite como DATACLK_OUT.

Mantener la alineación correcta de los datos y el reloj es un reto común con los DAC de alta velocidad, complicado por los cambios de temperatura y otras condiciones de funcionamiento. El uso de la señal DATACLK_OUT para generar los datos permite anular la mayor parte de la variación interna de proceso, temperatura y retardo de tensión. El AD973x simplifica aún más este problema de captura de datos de alta velocidad con dos controladores de temporización adaptativos de bucle cerrado. Un controlador de temporización gestiona los datos LVDS y la alineación del reloj de datos (controlador LVDS), y el otro gestiona los datos LVDS y la alineación DACCLK (controlador de sincronización). El controlador LVDS localiza las transiciones de datos y retrasa el DATACLK_IN para que su transición esté en el centro de la ventana de datos válida. El controlador sync gestiona el FIFO que mueve los datos desde el dominio LVDS DATACLK_IN al dominio DACCLK. Ambos controladores pueden funcionar en modo manual bajo control externo del procesador, en modo vigilancia donde las condiciones de error generan interrupciones externas, o en modo automático donde los errores se corrigen automáticamente. Los controladores LVDS y sync incluyen filtrado de media móvil para inmunidad al ruido y umbrales variables para controlar la actividad. Normalmente, los controladores están configurados para funcionar en modo automático, realizando los ajustes necesarios sin dejar caer o duplicar el samplessent al DAC. Ambos controladores requieren una calibración inicial antes de entrar en modo de actualización automática. La salida analógica del AD973x cambia 35 ciclos DACCLK después de que cambien los datos de entrada en modo 1× con el FIFO desactivado. La FIFO añade hasta ocho ciclos adicionales de retardo. Este retardo se lee desde el puerto SPI. La variación del retardo del reloj interno es inferior a un solo ciclo DACCLK a 1,2 GHz (833 ps). Detener el DATACLK_IN del AD973x mientras el DACCLK sigue funcionando puede provocar señales de salida impredecibles. Esto ocurre porque la ruta de la señal digital interna está intercalada. Las dos últimas muestras sincronizadas en el DAC continúan siendo sincronizadas por DACCLK incluso después de que DATACLK_IN se haya detenido. La señal de salida resultante tiene una frecuencia de la mitad de fDAC, y la amplitud depende de la diferencia entre las dos últimas muestras. El control de las funciones del AD973x se realiza a través de los registros programados en serie listados en la Tabla 9. Opcionalmente, un número limitado de funciones pueden ser ajustadas directamente por pines externos en modo pin.