Descripción

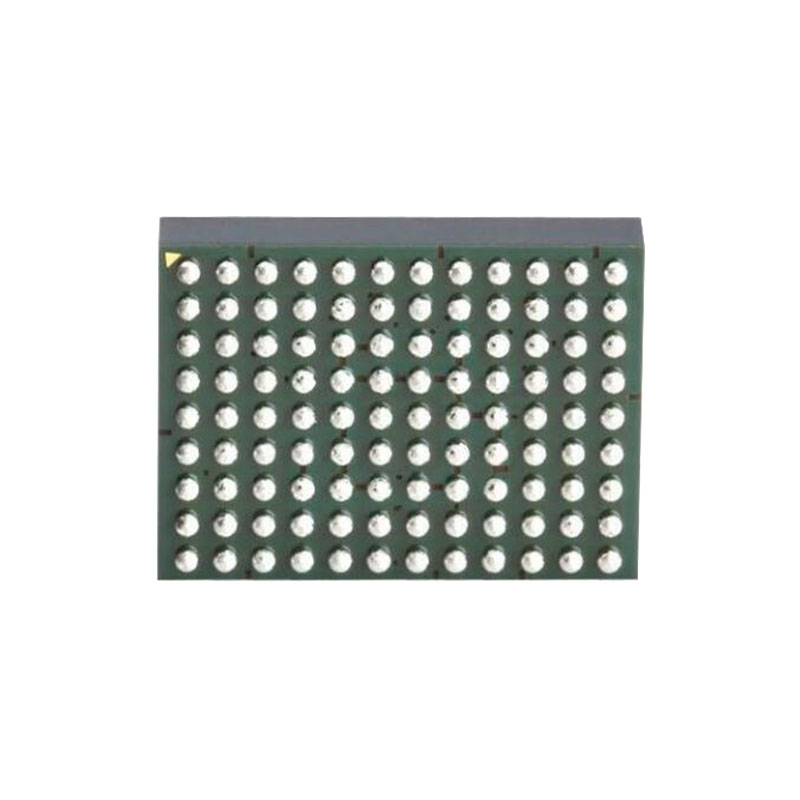

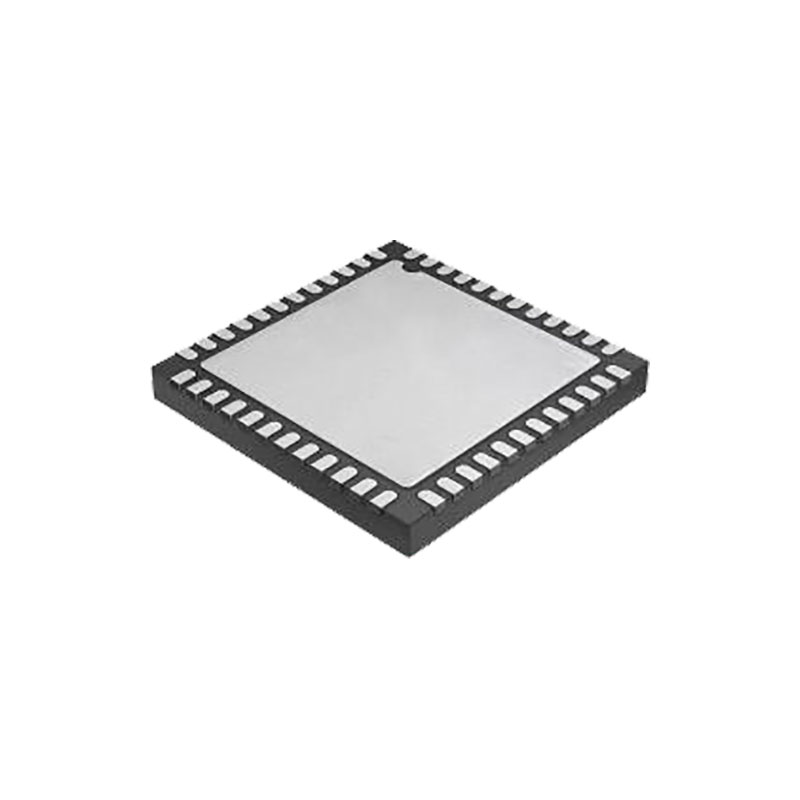

El AT24C256C proporciona 262.144 bits de memoria serie de sólo lectura programable y borrable eléctricamente (EEPROM) organizada en 32.768 palabras de 8 bits cada una. La función de conexión en cascada del dispositivo permite que hasta ocho dispositivos compartan un bus común de dos hilos. El dispositivo está optimizado para su uso en muchas aplicaciones industriales y comerciales en las que es esencial un funcionamiento de bajo consumo y bajo voltaje. Los dispositivos están disponibles en encapsulados SOIC de 8 terminales, TSSOP de 8 terminales, UDFN de 8 terminales y VFBGA de 8 terminales para ahorrar espacio. Todos los encapsulados funcionan de 1,7 V a 5,5 V.

Características

- Funcionamiento en baja tensión y tensión estándar:

- VCC = 1,7 V a 5,5 V

- Organizado internamente como 32.768 x 8 (256K)

- Temperatura industrial: -40°C a +85°C

- Interfaz serie compatible con I2C (dos hilos):

- 100 kHz Modo estándar, 1,7 V a 5,5 V

- 400 kHz Modo rápido, 1,7 V a 5,5 V

- Modo rápido Plus (FM+) de 1 MHz, de 2,5 V a 5,5 V

- Disparadores Schmitt, entradas filtradas para supresión de ruido

- Protocolo de transferencia bidireccional de datos

- Clavija de protección contra escritura para la protección completa de datos por hardware de la matriz

- Corriente activa ultrabaja (3 mA máximo) y corriente de espera (6 μA máximo)

- Modo de escritura de página de 64 bytes:

- Se permiten escrituras parciales de páginas

- Modos de lectura aleatoria y secuencial

- Ciclo de escritura automático en 5 ms como máximo

- Protección ESD >4.000 V

- Alta fiabilidad:

- Resistencia: 1.000.000 de ciclos de escritura

- Conservación de datos: 100 años

- Opciones de embalaje ecológico (sin plomo, sin haluro y conforme a la directiva RoHS)

- Opciones de venta de troqueles: Forma de oblea y obleas con protuberancias

Entradas de dirección de dispositivo (A0, A1, A2)

Los pines A0, A1 y A2 son entradas de dirección de dispositivo que están cableadas (directamente a GND o a VCC) para compatibilidad con otros dispositivos EEPROM serie de dos hilos. Cuando los pines están cableados, se pueden direccionar hasta ocho dispositivos en un único sistema de bus. Un dispositivo se selecciona cuando el hardware y el software coinciden. Si estos pines se dejan flotando, los pines A0, A1 y A2 se bajarán internamente a GND. Sin embargo, debido al acoplamiento capacitivo que puede aparecer en las aplicaciones del cliente, Microchip recomienda conectar siempre los pines de dirección a un estado conocido. Cuando utilice una resistencia de pull-up, Microchip recomienda utilizar 10 kΩ o menos.

Funcionamiento del dispositivo y comunicación

El AT24C256C funciona como un dispositivo cliente y utiliza una sencilla interfaz serie digital de dos hilos compatible con I2C para comunicarse con un controlador host, comúnmente denominado host de bus. El host inicia y controla todas las operaciones de lectura y escritura de los dispositivos cliente en el bus serie, y tanto el host como los dispositivos cliente pueden transmitir y recibir datos en el bus.

La interfaz serie se compone sólo de dos líneas de señal: Reloj serie (SCL) y Datos serie (SDA). El pin SCL se utiliza para recibir la señal de reloj del host, mientras que el pin bidireccional SDA se utiliza para recibir información de comandos y datos del host, así como para enviar datos de vuelta al host. Los datos siempre se enclavan en el AT24C256C en el flanco ascendente de SCL y siempre salen del dispositivo en el flanco descendente de SCL. Los pines SCL y SDA incorporan filtros de supresión de picos integrados y disparadores Schmitt para minimizar los efectos de los picos de entrada y el ruido del bus.

Toda la información de comandos y datos se transfiere con el bit más significativo (MSb) en primer lugar. Durante la comunicación por bus, se transmite un bit de datos cada ciclo de reloj, y después de que se hayan transferido ocho bits (un byte) de datos, el dispositivo receptor debe responder con un bit de respuesta de reconocimiento (ACK) o de no reconocimiento (NACK) durante un noveno ciclo de reloj (ciclo de reloj ACK/NACK) generado por el host. Por lo tanto, se necesitan nueve ciclos de reloj por cada byte de datos transferido. No hay ciclos de reloj no utilizados durante ninguna operación de lectura o escritura, por lo que no debe haber interrupciones o pausas en el flujo de datos durante cada transferencia de byte de datos y ciclo de reloj ACK o NACK.

Durante las transferencias de datos, los datos en el pin SDA sólo deben cambiar mientras SCL está bajo y los datos deben permanecer estables mientras SCL está alto. Si los datos en el pin SDA cambian mientras SCL está alto, entonces ocurrirá una condición de Inicio o de Paro. Las condiciones de Start y Stop se utilizan para iniciar y finalizar todas las comunicaciones del bus serie entre el host y los dispositivos cliente. El número de bytes de datos transferidos entre una condición de Inicio y una de Paro no está limitado y es determinado por el host. Para que el bus serie esté inactivo, ambos pines SCL y SDA deben estar en estado lógico alto al mismo tiempo.