Descripción:

CY7C027 y CY7C028 son RAM estáticas CMOS de 32K, 64K × 16 de doble puerto y bajo consumo. Los dispositivos incluyen varios esquemas de arbitraje para manejar situaciones en las que varios procesadores acceden a la misma pieza de datos. Se proporcionan dos puertos, lo que permite un acceso independiente y asíncrono para lecturas y escrituras en cualquier ubicación de la memoria. Los dispositivos pueden utilizarse como RAM estáticas independientes de doble puerto de 16 bits o pueden combinarse varios dispositivos para funcionar como RAM estáticas de doble puerto maestro/esclavo de 32 bits o más. Se proporciona una patilla M/S para implementar aplicaciones de memoria de 32 bits o más sin necesidad de dispositivos maestro y esclavo independientes o lógica discreta adicional. Las áreas de aplicación incluyen diseños interprocesador y multiprocesador, búfer de estado de comunicaciones y memoria de vídeo/gráficos de doble puerto.

Cada puerto tiene pines de control independientes: doble habilitación de chip (CE0 y CE1), habilitación de lectura o escritura (R/W) y habilitación de salida (OE). Cada puerto dispone de dos indicadores (BUSY e INT). BUSY indica que el puerto está intentando acceder a la misma ubicación a la que está accediendo el otro puerto. La bandera de interrupción (INT) permite la comunicación entre puertos o sistemas mediante un buzón. Los semáforos se utilizan para pasar una bandera, o token, de un puerto al otro para indicar que un recurso compartido está en uso. La lógica del semáforo se compone de ocho latches compartidos. Sólo un lado puede controlar el latch (semáforo) en cualquier momento. El control de un semáforo indica que se está utilizando un recurso compartido. La función de apagado automático se controla de forma independiente en cada puerto mediante los pines de habilitación del chip.

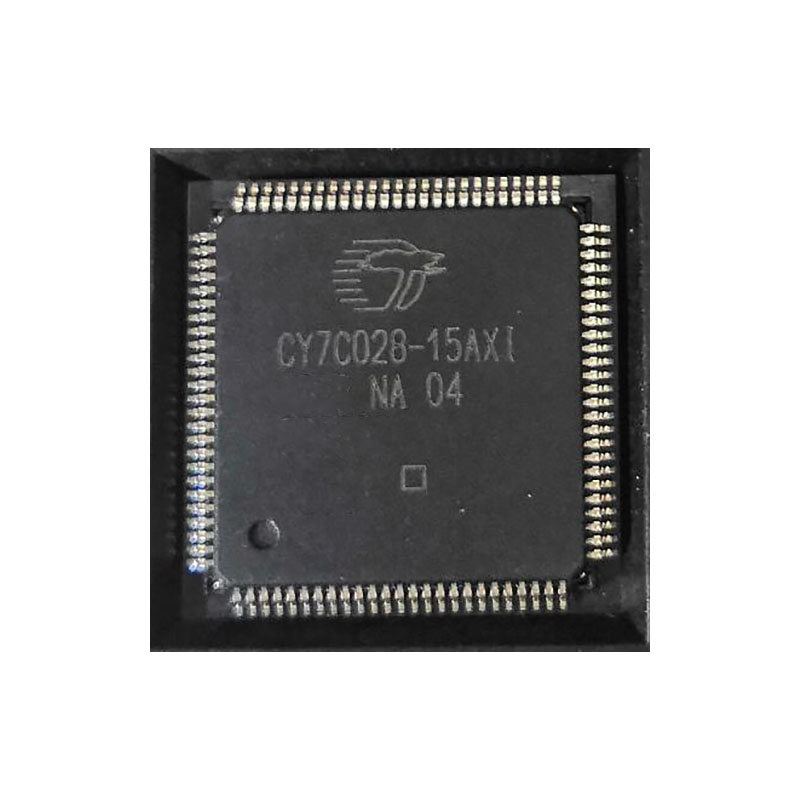

CY7C027 y CY7C028 están disponibles en encapsulados TQFP (Thin Quad Flat pack) de 100 patillas.

Los CY7C027 y CY7C028 son Obsoleto

Características:

Células de memoria de doble puerto que permiten el acceso simultáneo a la misma posición de memoria.

Organización 64K × 16 (CY7C028)

CMOS de 0,35 micras para una velocidad y potencia óptimas

Acceso de alta velocidad: 15 y 20 ns

Baja potencia de funcionamiento

Activo: ICC = 180 mA (típico)

En espera: ISB3 = 0,05 mA (típico)

Funcionamiento totalmente asíncrono

Apagado automático

Bus de datos ampliable a 32 bits o más mediante la selección de chip maestro/esclavo cuando se utiliza más de un dispositivo.

Lógica de arbitraje en chip

Semáforos incluidos para permitir el handshaking de software entre puertos.

Indicadores INT para la comunicación puerto a puerto

Control separado de byte superior e inferior

El doble chip permite

Selección de pin para maestro o esclavo

Rangos de temperatura comercial e industrial

Disponible en TQFP de 100 patillas

Envases sin Pb disponibles

Modo de retención de datos:

Los modelos CY7C027 y CY7C028 se han diseñado teniendo en cuenta las baterías de reserva. La tensión de retención de datos y la corriente de alimentación están garantizadas por encima de la temperatura. Las siguientes reglas aseguran la retención de datos:

- La habilitación de chip (CE) debe mantenerse ALTA durante la retención de datos, dentro de VCC a VCC - 0,2 V.

- CE debe mantenerse entre VCC - 0,2 V y 70% de VCC durante las transiciones de encendido y apagado.

- La RAM puede empezar a funcionar > tRC después de que VCC alcance la tensión mínima de funcionamiento (4,5 V).

NOTAS:

Probados inicialmente y después de cualquier cambio de diseño o proceso que pueda afectar a estos parámetros.

CE = VCC, VIN = GND a VCC, TA = 25 °C. Este parámetro está garantizado pero no probado.

Arquitectura:

Los CY7C027 y CY7C028 constan de una matriz de 32K y 64K palabras de 16 bits cada una de células RAM de doble puerto, líneas de E/S y dirección, y señales de control (CE, OE, R/W). Estos pines de control permiten el acceso independiente para lecturas o escrituras en cualquier posición de la memoria. Para manejar escrituras/lecturas simultáneas en la misma posición, se proporciona un pin BUSY en cada puerto. Se pueden utilizar dos pines de interrupción (INT) para la comunicación puerto a puerto. Dos pines de control de semáforo (SEM) se utilizan para asignar recursos compartidos. Con el pin M/S, los dispositivos pueden funcionar como maestro (los pines BUSY son salidas) o como esclavo (los pines BUSY son entradas). Los dispositivos también disponen de una función de apagado automático controlada por CE. Cada puerto dispone de su propio control de habilitación de salida (OE), que permite leer datos del dispositivo.