DESCRIPCIÓN GENERAL

El HMC903LP3E es un circuito integrado de microondas monolítico (MMIC) de arseniuro de galio (GaAs) autoalimentado, pseudomórfico (pHEMT), amplificador de bajo ruido (LNA) con un control de polarización opcional para la reducción de IDQ. Está alojado en un encapsulado LFCSP de 16 terminales y 3 mm × 3 mm. El amplificador HMC903LP3E funciona de 6 GHz a 17 GHz, proporcionando 18,5 dB de ganancia de señal pequeña y 1,7 dB de figura de ruido en la banda de 6 GHz a 16 GHz, y un IP3 de salida de 25 dBm en toda la banda de 6 GHz a 17 GHz, al tiempo que requiere sólo 80 mA de una alimentación de 3,5 V.

La potencia de salida P1dB de 14,5 dBm permite al LNA funcionar como controlador de oscilador local (LO) para mezcladores balanceados, I/Q o de rechazo de imagen. El HMC903LP3E también cuenta con una entrada y una salida bloqueadas en CC y adaptadas internamente a 50 Ω, lo que lo hace ideal para radios de microondas de alta capacidad y aplicaciones de vídeo por satélite (VSAT).

CARACTERÍSTICAS

Bajo factor de ruido: 1,7 dB típico entre 6 GHz y 16 GHz

Alta ganancia: 18,5 dB típicos de 6 GHz a 16 GHz

Potencia de salida para compresión de 1 dB (P1dB): 14,5 dBm típica de 6 GHz a 16 GHz

Tensión de alimentación única: 3,5 V a 80 mA típicos

Intercepción de tercer orden de salida (IP3): 25 dBm típico

50 Ω entrada/salida adaptadaETRETR

Auto polarizado con control de polarización opcional para reducción de I DQ

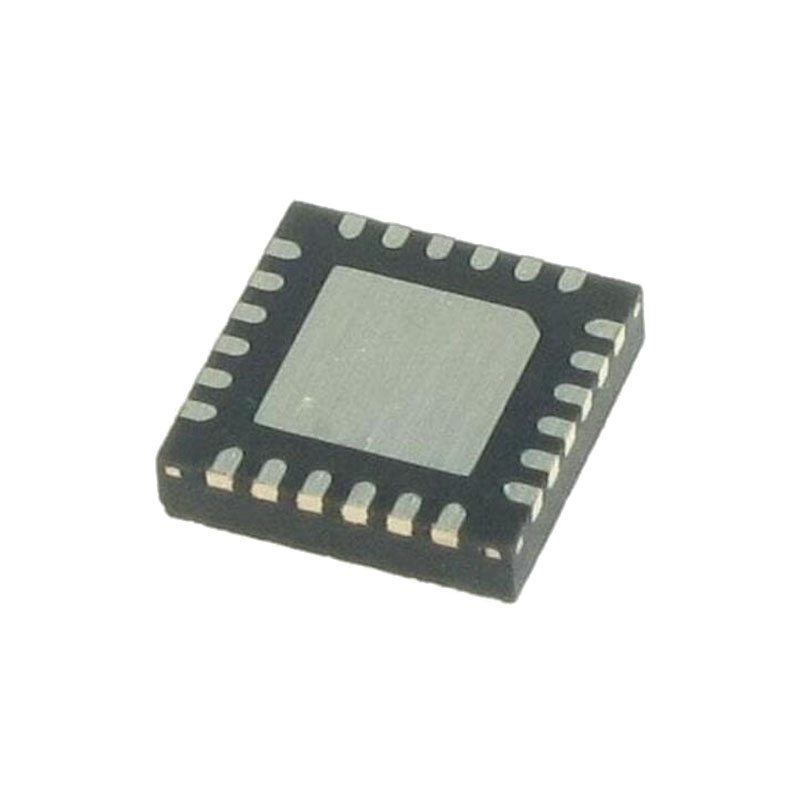

Encapsulado LFCSP de 16 terminales, 3 mm × 3 mm

APLICACIONES

Radios punto a punto

Radios punto a multipunto

Militar y espacial

Instrumentos de prueba

TEORÍA DE FUNCIONAMIENTO

TEORÍA DE FUNCIONAMIENTO El HMC903LP3E es un circuito integrado de microondas monolítico (MMIC) de arseniuro de galio (GaAs), pseudomórfico (pHEMT), amplificador de bajo ruido. El amplificador HMC903LP3E utiliza dos etapas de ganancia en serie, y el esquema básico del amplificador , que forma un amplificador de bajo ruido que opera desde 6 GHz a 17 GHz con un excelente rendimiento de la figura de ruido.

El HMC903LP3E tiene puertos de entrada y salida de terminación única cuyas impedancias son nominalmente iguales a 50 Ω en el rango de frecuencias de 6 GHz a 17 GHz. En consecuencia, se puede insertar directamente en un sistema de 50 Ω sin necesidad de circuitos de adaptación de impedancias, lo que también significa que se pueden conectar en cascada varios amplificadores HMC903LP3E sin necesidad de circuitos de adaptación externos.

Las impedancias de entrada y salida son lo suficientemente estables frente a las variaciones de temperatura y tensión de alimentación como para no necesitar compensación de adaptación de impedancias.

Tenga en cuenta que es fundamental suministrar conexiones a tierra de muy baja inductancia a los pines GND y a la almohadilla expuesta de la base del paquete para garantizar un funcionamiento estable. Para lograr un rendimiento óptimo de la HMC903LP3E y para evitar daños en el dispositivo, no exceda los valores máximos absolutos.

INFORMACIÓN SOBRE APLICACIONES

Las conexiones básicas para operar el HMC903LP3E. Tanto los puertos RFIN y RFOUT tienen condensadores de bloque de CC en el chip que eliminan la necesidad de condensadores de acoplamiento de CA externos.

El HMC903LP3E tiene pines opcionales de polarización de puerta VGG1 y VGG2. Cuando estas patillas se dejan abiertas, el amplificador funciona en polarización automática con un IDQ típico = 80 mA, cuando VDD1 /VDD2 = 3,5 V. Cuando utilice las patillas de polarización de puerta VGG1 y VGG2, siga la secuencia de polarización recomendada para no dañar el amplificador.

SECUENCIA DE POLARIZACIÓN RECOMENDADA DURANTE EL ENCENDIDO

La secuencia de polarización recomendada para encender el HMC903LP3E es la siguiente:

- Conectar a GND.

- Ajuste VGG1 y VGG2 a -2 V.

3.Ajuste VDD1 y VDD2 a 3,5 V.

- Aumente VGG1 y VGG2 para conseguir un IDQ típico = 80 mA.

- Aplique la señal de radiofrecuencia.

SECUENCIA DE POLARIZACIÓN RECOMENDADA DURANTE EL APAGADO

La secuencia de polarización recomendada para apagar el HMC903LP3E es la siguiente:

- Apague la señal de radiofrecuencia.

- Disminuya VGG1 y VGG2 a -2 V para conseguir un IDQ típico = 0 mA.

- Disminuya VDD1 y VDD2 a 0 V.

- Aumentar VGG1 y VGG2 a 0 V.

A menos que se indique lo contrario, todas las medidas y datos mostrados se tomaron utilizando el circuito de aplicación típico, con la placa de evaluación y polarizados según las condiciones de esta sección. Los pines VDD1 y VDD2 están conectados entre sí; del mismo modo, los pines VGG1 y VGG2 también están conectados entre sí. Las condiciones de polarización mostradas en esta sección son los puntos de funcionamiento recomendados para optimizar el rendimiento global. El uso de otras condiciones de polarización puede proporcionar un rendimiento diferente al mostrado en esta hoja de datos.