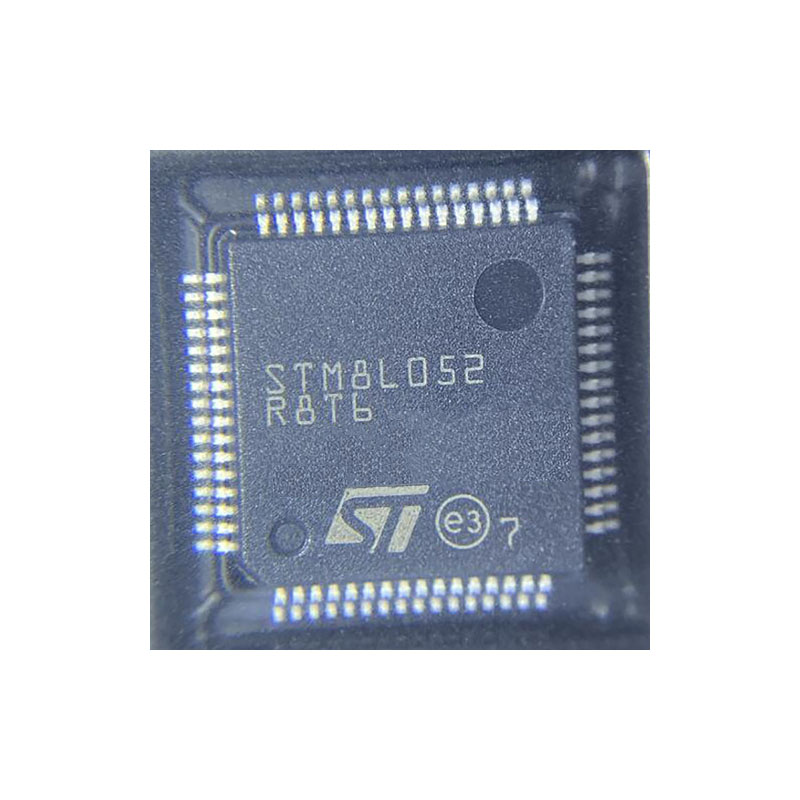

Descripción

La familia de ultra bajo consumo STM8L05xxx de la línea económica incorpora el núcleo de CPU STM8 mejorado que proporciona una mayor potencia de procesamiento (hasta 16 MIPS a 16 MHz) al tiempo que mantiene las ventajas de una arquitectura CISC con densidad de código mejorada, un espacio de direccionamiento lineal de 24 bits y una arquitectura optimizada para operaciones de bajo consumo.

La familia incluye un módulo de depuración integrado con una interfaz de hardware (SWIM) que permite una depuración no intrusiva en la aplicación y una programación Flash ultrarrápida.

Los microcontroladores STM8L05xxx de la línea de valor de alta densidad incorporan EEPROM de datos y memoria Flash de programación de bajo consumo, bajo voltaje y alimentación única.

Todos los dispositivos ofrecen ADC de 12 bits, reloj en tiempo real, cuatro temporizadores de 16 bits, un temporizador de 8 bits, así como interfaz de comunicación estándar como dos SPI, I2C, tres USART y LCD de 8×24 o 4×28 segmentos. El LCD de 8×24 o 4x 28 segmentos está disponible en la línea de valor de alta densidad STM8L05xxx.

La familia STM8L05xxx funciona de 1,8 V a 3,6 V y está disponible en el rango de temperatura de -40 a +85 °C.

El diseño modular del conjunto de periféricos permite encontrar los mismos periféricos en diferentes familias de microcontroladores ST, incluidas las familias de 32 bits. Esto hace que cualquier transición a una familia diferente sea muy fácil, y simplificada aún más por el uso de un conjunto común de herramientas de desarrollo.

Todos los productos STM8L de ultra bajo consumo de la línea value se basan en la misma arquitectura, con la misma asignación de memoria y un pinout coherente.

Características:

- Condiciones de funcionamiento

- Alimentación de funcionamiento: 1,8 V a 3,6 V

- Temperatura: de -40 °C a 85 °C

- Funciones de bajo consumo

- 5 modos de bajo consumo: Espera, Marcha de bajo consumo (5,9 µA), Espera de bajo consumo (3 µA), Parada activa con RTC completo (1,4 µA), Parada (400 nA)

- Consumo dinámico: 200 µA/MHz + 330 µA

- Fugas ultrabajas por I/0: 50 nA

- Despertar rápido desde parada: 4,7 µs

- Núcleo STM8 avanzado

- Arquitectura Harvard y pipeline de 3 etapas

- Frecuencia máx. 16 MHz, 16 MIPS CISC pico

- Hasta 40 fuentes de interrupción externas

- Reajuste y gestión de suministros

- Reinicio BOR de bajo consumo y ultraseguro con 5 umbrales programables

- POR/PDR de muy bajo consumo

- Detector de tensión programable (PVD)

- Gestión del reloj

- Osciladores de cristal de 32 kHz y 1 a 16 MHz

- RC interno de 16 MHz ajustado en fábrica

- 38 kHz bajo consumo RC

- Sistema de seguridad del reloj

- RTC de bajo consumo

- Calendario BCD con interrupción de alarma

- Calibración digital con una precisión de +/- 0,5 ppm

- Detección antimanipulación avanzada

- LCD: 8×24 o 4×28 con convertidor elevador

- Recuerdos

- 64 KB de memoria de programa Flash y 256 bytes de EEPROM de datos con ECC, RWW

- Modos flexibles de protección contra escritura y lectura

- 4 KB de RAM

DMA

- 4 canales compatibles con ADC, SPI, I2C, USART y temporizadores

- 1 canal de memoria a memoria

- ADC de 12 bits de hasta 1 Msps/27 canales

- Tensión de referencia interna

- Temporizadores

- Tres temporizadores de 16 bits con 2 canales (utilizados como IC, OC, PWM), codificador de cuadratura

- Un temporizador de control avanzado de 16 bits con 3 canales, compatible con el control del motor

- Un temporizador de 8 bits con preescalador de 7 bits

- 2 perros guardianes: 1 Ventana, 1 Independiente

- Temporizador sonoro con frecuencias de 1, 2 ó 4 kHz

- Interfaces de comunicación

- Dos interfaces serie síncronas (SPI)

- I2C rápido 400 kHz SMBus y PMBus

- Tres USART (interfaz ISO 7816 + IrDA)

- Hasta 54 E/S, todas asignables a vectores de interrupción

- Apoyo al desarrollo

- Programación rápida en el chip y depuración no intrusiva con SWIM

- Cargador de arranque mediante USART

Rendimiento

Todas las familias incorporan núcleos de alta eficiencia energética tanto con arquitectura Harvard como con ejecución en pipelines: núcleo avanzado STM8 para las familias STM8L y núcleo ARM Cortex™-M3 para la familia STM32L. Además, se ha prestado especial atención al diseño de la arquitectura para optimizar las relaciones mA/DMIPS y mA/MHz.

Esto permite que el rendimiento de ultra bajo consumo oscile entre 5 y 33,3 DMIP.

Periféricos compartidos

STM8L05x, STM8L15x y STM32L15xx comparten periféricos idénticos que garantizan una migración muy sencilla de una familia a otra:

- Periférico analógico: ADC1

- Periféricos digitales: RTC y algunas interfaces de comunicación