DESCRIPTION

Le M24C01(C02) est une EEPROM (mémoire programmable effaçable électriquement) compatible I2C de 1(2) Kbit, organisée en 128 (256) × 8 bits.

Le M24C01/02-W est accessible avec une tension d'alimentation de 2,5 V à 5,5 V, le M24C01/02-R est accessible avec une tension d'alimentation de 1,8 V à 5,5 V, et le M24C02-F est accessible soit avec une tension d'alimentation de 1,7 V à 5,5 V (sur toute la plage de température), soit avec une tension d'alimentation étendue de 1,6 V à 5,5 V dans certaines conditions restreintes. Ces dispositifs fonctionnent avec une fréquence d'horloge maximale de 400 kHz.

CARACTÉRISTIQUES

Interface I²C

- Compatible avec les modes de bus I²C suivants :

- 400 kHz (mode rapide)

- 100 kHz (mode standard)

Mémoire

- 1 kbit (128 octets) d'EEPROM

- 2-Kbit (256-byte) d'EEPROM

- Taille de la page : 16 octets

Tension d'alimentation

- Large plage de tension : De 1,6 V à 5,5 V

- M24C01/02-W : 2,5 V à 5,5 V

- M24C01/02-R : 1,8 V à 5,5 V

- M24C02-F:1,7 V à 5,5 V , 1,6 V à 5,5 V (sous contrainte de température)

Température

- Plage de température de fonctionnement : de -40 °C à +85 °C

Temps de cycle d'écriture rapide

- Écriture d'octets et de pages dans un délai de 5 ms

Performance

- Protection renforcée contre les décharges électrostatiques (ESD) et le verrouillage

- Plus de 4 millions de cycles d'écriture

- Conservation des données pendant plus de 200 ans

Fonctionnalités avancées

- Modes de lecture aléatoire et séquentielle

- Protection matérielle en écriture de l'ensemble de la matrice de mémoire

- Protection renforcée contre les décharges électrostatiques (ESD) et le verrouillage

Emballages conformes à la directive RoHS et sans halogène

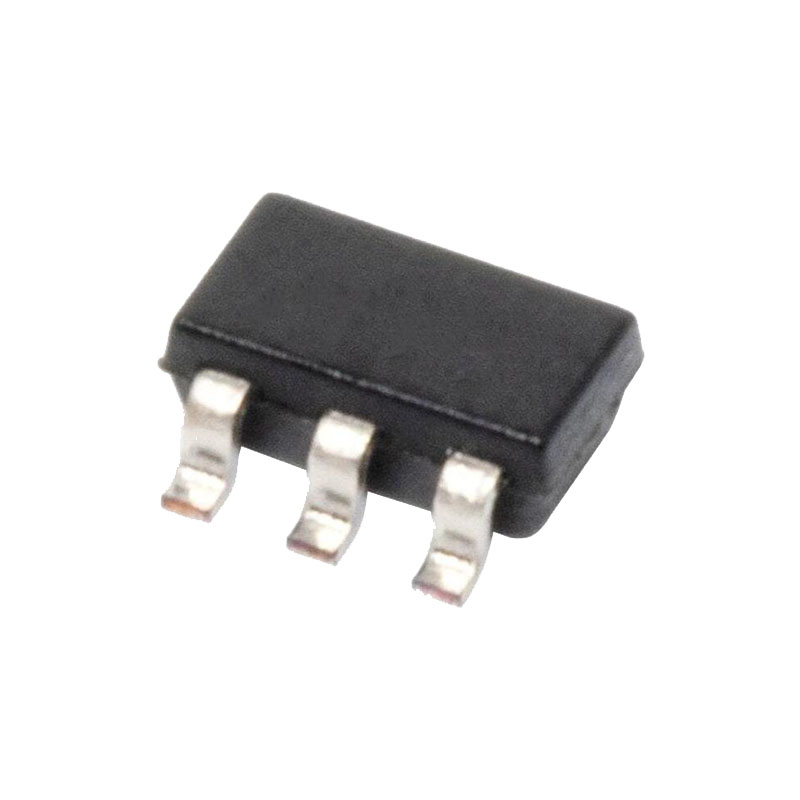

- SO8N (ECOPACK2)

- TSSOP8 (ECOPACK2)

- UFDFPN8 (ECOPACK2)

- UFDFPN5 (ECOPACK2)

DESCRIPTION DU SIGNAL

Horloge série (SCL)

Le signal appliqué sur l'entrée SCL est utilisé pour strober les données disponibles sur SDA(in) et pour sortir les données sur SDA(out).

Données sérielles (SDA)

SDA est une entrée/sortie utilisée pour transférer des données en entrée ou en sortie de l'appareil. SDA(out) est une sortie à drain ouvert qui peut être câblée avec d'autres signaux à drain ouvert ou à collecteur ouvert sur le bus. Une résistance pull-up doit être connectée entre les données série (SDA) et VCC.

Tension d'alimentation de fonctionnement (VCC)

Avant de sélectionner la mémoire et d'y envoyer des instructions, il convient d'obtenir une valeur VCC dans les limites de la tension spécifiée [VCC(min), VCC(max)] doit être appliquée. Afin d'assurer une tension d'alimentation continue stable, il est recommandé de découpler l'alimentation VCC avec un condensateur approprié (généralement de l'ordre de 10 nF à 100 nF) proche de la ligne VCC/VSS broches de l'emballage.

Cette tension doit rester stable et valide jusqu'à la fin de la transmission de l'instruction et, pour une instruction d'écriture, jusqu'à la fin du cycle d'écriture interne (tW).

Réinitialisation du dispositif

Afin d'éviter les opérations d'écriture par inadvertance lors de la mise sous tension, un circuit de réinitialisation à la mise sous tension (POR) est inclus.

Lors de la mise sous tension, le dispositif ne répond à aucune instruction jusqu'à ce que VCC a atteint la tension de seuil de réinitialisation interne. Ce seuil est inférieur à la tension minimale de VCC tension de fonctionnement. Lorsque VCC dépasse le seuil POR, l'appareil est réinitialisé et passe en mode d'alimentation de secours ; toutefois, il ne faut pas accéder à l'appareil avant que VCC atteint une tension continue valide et stable à l'intérieur des limites spécifiées [VCC(min), VCC(max)] gamme .

De la même manière, lors de la mise hors tension (diminution continue de VCC), le dispositif ne doit pas être accessible lorsque VCC descend en dessous de VCC(min). Lorsque VCC descend en dessous du seuil de réinitialisation, l'appareil ne répond plus à aucune instruction qui lui est envoyée.

Conditions de mise hors tension

Pendant la mise hors tension (diminution continue de VCC), l'appareil doit être en mode veille (mode atteint après le décodage d'une condition d'arrêt, en supposant qu'aucun cycle d'écriture interne n'est en cours).

Opérations de lecture

Les opérations de lecture sont effectuées indépendamment de l'état du signal de commande d'écriture (WC).

Pour les instructions de lecture, après chaque octet lu (sortie de données), l'appareil attend un accusé de réception (entrée de données) pendant le 9e temps binaire. Si le maître du bus n'accuse pas réception pendant ce 9e temps, l'appareil met fin au transfert de données et passe en mode d'attente après une condition d'arrêt.