概要

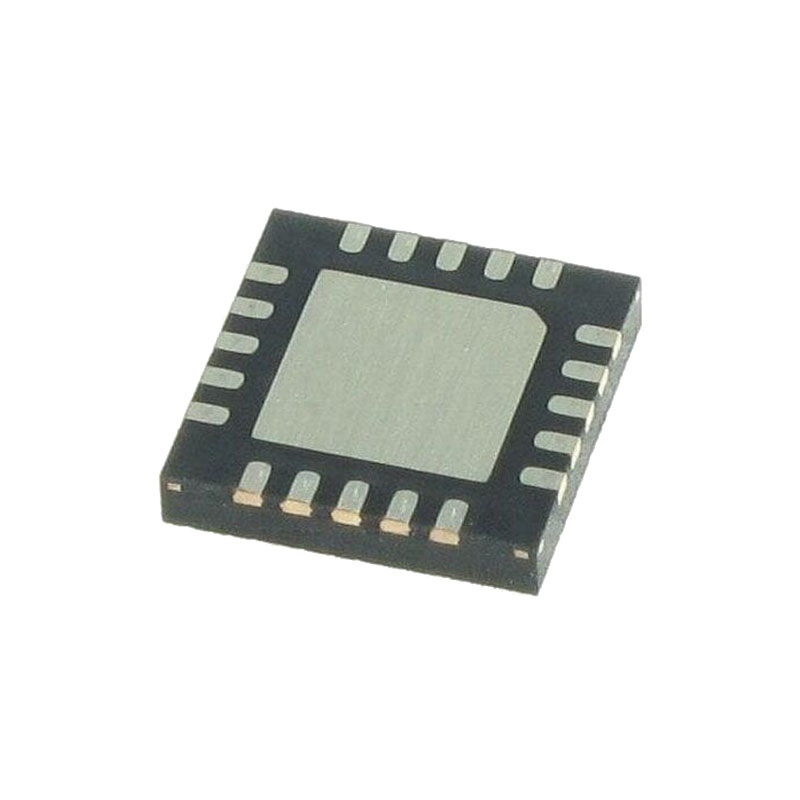

AD5360/AD5361 は 16/14 ビット DAC を 1 個の 52 ピン LQFP または 56 ピン LFCSP パッケージに内蔵しています。これらの DAC は、基準電圧の 4 倍のスパンのバッファード電圧出力を提供します。各DACのゲインおよびオフセットは、独立にトリミングして誤差を除去できます。さらに柔軟性を高めるため、このデバイスは8個のDACから成る2つのグループに分割され、各グループの出力範囲はオフセットDACによって独立して調整できます。

AD5360/AD5361 は、VSS が -4.5 V ~ -16.5 V、VDD が +8 V ~ +16.5 V の広い電源範囲で動作を保証しています。出力アンプのヘッドルーム要件は 1.4 V です。

AD5360/AD5361 は SPI、QSPI™、MICROWIRE™、DSP インターフェース規格と 互換性のある高速 4 線シリアル・インターフェースを持ち、最大 50 MHz のクロック速度を扱うことができます。LDAC入力をLowにすることで、すべての出力を同時に更新できます。各チャンネルには、プログラマブル・ゲイン・レジスタとオフセット調整レジスタがあります。

各DAC出力は増幅され、外部SIGGNDx入力に対してオンチップ・バッファリングされる。DAC出力は、CLRピンを介してSIGGNDxに切り替えることもできる。

特徴

52ピンLQFPおよび56ピンLFCSPパッケージの16チャンネルDAC

16/14ビットまで単調保証

公称出力電圧範囲 -10 V~+10 V

複数の出力スパンが利用可能

温度モニタリング機能

チャンネル・モニタリング・マルチプレクサ

GPIO機能

オフセットとゲインをユーザーがプログラム可能なシステム・キャリブレーション機能

チャンネルのグループ化とアドレス指定機能

データ・エラー・チェック機能

SPI互換シリアルインターフェース

2.5 V~5.5 Vデジタル・インターフェース

デジタルリセット(RESET)

ユーザー定義SIGGNDxへのクリア関数

DAC出力の同時更新

アプリケーション

計装

産業用制御システム

自動試験装置(ATE)におけるレベル設定

可変光減衰器(VOA)

光ラインカード

機能的

説明 DACアーキテクチャ

AD5360/AD5361 は 16 個の DAC チャンネルと 16 個の出力アンプを 1 つのパッケー ジに内蔵しています。1 つの DAC チャンネルのアーキテクチャは、AD5360 の場合は 16 ビットの抵抗ストリング DAC、AD5361 の場合は 14 ビットの DAC と、それに続く出力バッファー・アンプで構成されます。抵抗ストリング・セクションは、VREF0 または VREF1 から AGND までの単純に等しい値の抵抗のストリングです。このタイプのアーキテクチャは、DACの単調性を保証する。DACレジスタにロードされた16ビット/14ビットのバイナリ・デジタル・コードにより、出力アンプに供給される前に、ストリング上のどのノードで電圧がタップオフされるかが決定される。出力アンプはDAC出力電圧を4逓倍する。公称出力スパンは、3V基準で12V、5V基準で20Vである。

チャンネル・グループ

AD5360/AD5361 の 16 個の DAC チャンネルは 8 チャンネルずつの 2 つのグ ループに分かれています。グループ 0 の 8 個の DAC は VREF0 から基準電圧を得ます。グループ 1 は VREF1 から基準電圧を得ます。各グループはそれ自身の信号グランド・ピンを持っています。

A/Bレジスタのゲイン/オフセット調整

各 DAC チャンネルには 7 つのデータ・レジスタがある。実際の DAC データ・ワードは、コントロール・レジスタの A/B ビットの設定に応じて、X1A または X1B 入力レジスタのいずれかに書き込まれる。A/B ビットが 0 の場合、データは X1A レジスタに書き込まれる。A/B ビットが 1 の場合、データは X1B レジスタに書き込まれる。この単一ビットはグローバル・コントロールであり、デバイスのすべての DAC チャンネルに影響することに注意してください。ある書き込みが X1A レジスタに、ある書き込みが X1B レジスタになるように、デバイスをチャンネル毎に設定することはできない。

各 DAC チャンネルには、ゲイン・レジスタ(M)とオフセット・レジスタ(C)もあり、信号チェーン全体のゲイン誤差とオフセット誤差をトリミングすることができる。X1Aレジスタからのデータは、デジタル乗算器と加算器によって、MとCレジスタの内容で演算される。校正された DAC データは、X2A レジスタに格納されます。同様に、X1B レジスタからのデータは乗算器と加算器で演算され、X2B レジスタに格納されます。

各チャンネルに乗算器と加算器のシンボルが示されているが、デバイスには乗算器と加算器が1つずつしかなく、全チャンネルで共有されている。このことは、「レジスタ更新レート」セクションで説明するように、複数のチャネルを一度に更新する場合の更新速度に影響する。

データが X1A レジスタ、または A/B 制御ビットが 0 に設定された M または C レジスタに書き込まれる度に、X2A データが再計算され、X2A レジスタが自動的に更新される。同様に、X1B または A/B が 1 に設定された M または C レジスタにデータが書き込まれる度に、X2B が更新される。

X2A および X2B レジスタから出力されたデータは、マルチプレクサによって最後の DAC レジスタにルーティングされる。8つのDACの各グループに関連付けられた8ビットのA/Bセレクト・レジスタは、個々のDACがX2AレジスタとX2Bレジスタのどちらからデータを取得するかを制御する。このレジスタのビットが0の場合、DACはX2Aレジスタからデータを取得し、1の場合、DACはX2Bレジスタからデータを取得する(ビット0~ビット7は、それぞれDAC0~DAC7を制御する)。

2つのレジスタに16ビットがあるため、各DACがX2AレジスタとX2Bレジスタのどちらからデータを取得するかをチャネルごとに設定することが可能であることに注意されたい。A/Bセレクト・レジスタの全ビットを0または1に設定するグローバル・コマンドも提供される。

AD5360/AD5361 のすべての DAC は、各 DAC レジスタがその X2A または X2B レジスタ(A/B セレクト・レジスタの設定に依存する)から更新される時、LDAC をロー・レベルにする事により同時に更新する事ができます。DAC レジスタはユーザーによって読み出したり、直接書き込んだりするこ とはできません。