ОБЩЕЕ ОПИСАНИЕ

ADF4368 - это высокопроизводительный, с ультранизким джиттером, целочисленный-N и дробный-N цикл с фазовой автоподстройкой (PLL) со встроенным VCO, идеально подходящий для приложений преобразования частоты.

Высокопроизводительный PLL имеет коэффициент полезного действия -239 дБс/Гц, очень низкий уровень шума 1/f с нормированным значением -287 дБс/Гц и высокую частоту PFD, что позволяет достичь сверхнизкого уровня внутриполосного шума и интегрального джиттера. ADF4368 может генерировать любую частоту от 800 МГц до 12,8 ГГц без внутреннего удвоителя, что устраняет необходимость в фильтрах субгармоник. Модулятор Σ-Δ включает 25-битный фиксированный модуль, обеспечивающий герцовое разрешение частоты, и дополнительный 17-битный переменный модуль, позволяющий получить еще более тонкое разрешение и гибкость при планировании частоты. Выходная мощность 9 дБм на частоте 12,8 ГГц в односторонней конфигурации с функцией 16-ступенчатой регулировки мощности делает его очень полезным для любых приложений.

В приложениях с множественным преобразованием частоты, таких как радары с фазовой решеткой или массивные системы MIMO, выходы нескольких ADF4368 могут быть выровнены с помощью входа SYNC или EZSync™. Метод EZSync используется в тех случаях, когда сложно точно распределить сигнал SYNC по всем устройствам. Для приложений, где требуется детерминированная задержка или возможность регулировки задержки, можно использовать программируемую задержку между эталоном и выходом с.

Простота блок-схемы ADF4368 облегчает время разработки благодаря упрощенной карте регистров последовательно-периферийного интерфейса (SPI), внешнему входу SYNC и повторяемому многокристальному выравниванию фаз как в целочисленном, так и в дробном режиме.

ОСОБЕННОСТИ

► Диапазон выходных частот: от 800 МГц до 12,8 ГГц

► Джиттер < 30 fsRMS fOUT = 9,001 ГГц, fREF = fPFD = 250 МГц, дробный режим

► Низкий уровень широкополосного фазового шума: -160 дБс/Гц на частоте 12,8 ГГц

► Технические характеристики PLL

► Нормированный уровень внутриполосного фазового шума

► -239 дБс/Гц: целочисленный режим, -237 дБс/Гц: дробный режим

► Нормированный уровень фазового шума 1/f

► -287 дБс/Гц: нормировано на 1 Гц

► -147 дБс/Гц: нормировано на 1 ГГц при частоте 10 кГц

► 625 МГц частота фазового детектора целочисленный режим

► 250 МГц частотный дробный режим фазового детектора

► 25-битный фиксированный, 49-битный комбинированный дробный модуль

► Опорная входная частота 4 ГГц

► Типичные всплески PFD на уровне -95 дБc

► Ссылка на характеристики задержки выхода

► Температурный коэффициент: 0,06 пс/°C

► Размер шага регулировки: <1 пс

► Выравнивание фазы многочипового выхода

► Через контакт SYNC или с помощью метода EZSync

► Источники питания 3,3 В и 5 В

► Поддержка инструмента проектирования петлевых фильтров ADIsimPLL™

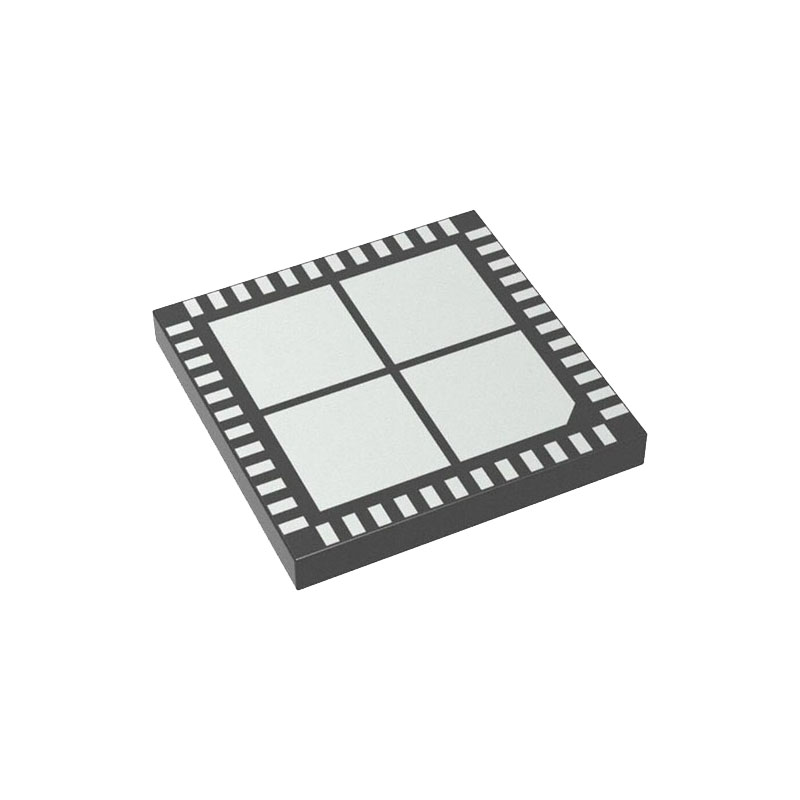

► Выпускается в 48-выводном корпусе LGA размером 7 мм × 7 мм

► Температура рабочего спая от -40°C до +125°C

ПРИЛОЖЕНИЯ

► Беспроводная инфраструктура (MC-GSM, 5G)

► Испытания и измерения

► Аэрокосмическая и оборонная промышленность

ИНФОРМАЦИЯ О ПРИЛОЖЕНИЯХ

ИСТОЧНИК ПИТАНИЯ И ШУНТИРОВАНИЕ

ADF4368 - это высокопроизводительное, малошумящее устройство. Фазовые шумы и помехи могут ухудшаться из-за шумных источников питания. Для достижения максимальной производительности и обеспечения того, чтобы шум источника питания не ухудшал характеристики ADF4368, рекомендуется использовать малошумящие регуляторы Analog Devices с высоким коэффициентом отклонения мощности источника питания (PSRR). Предпочтительные регуляторы включают LT3045, ADM7150 и ADM7151. Также рекомендуется использовать дополнительные шунтирующие конденсаторы внешнего питания. Более подробную информацию см. в проекте оценочной платы EVAL-ADF4368.

КОНСТРУКЦИЯ ПЕТЛЕВОГО ФИЛЬТРА

Стабильная конструкция петлевого фильтра требует тщательного выбора компонентов петлевого фильтра ADF4368. Для проектирования и моделирования петлевых фильтров рекомендуется загрузить и установить программу ADIsimPLL™. ADI simPLL™ имеет встроенный учебник для начинающих пользователей и справочное руководство для более сложных тем. Кроме того, на сайте www.analog.com доступно несколько обучающих видеороликов по ADIsimPLL. После разработки и моделирования петлевого фильтра рекомендуется проверить новый петлевой фильтр с помощью оценочного оборудования ADF4368.

Полное руководство по проектированию петлевых фильтров выходит за рамки данного технического описания. Однако некоторые лучшие практики приведены в следующих списках. ADIsimPLL помогает в определении и моделировании этих параметров. Любое значительное изменение этих параметров требует новой конструкции петлевого фильтра.