ОБЩЕЕ ОПИСАНИЕ

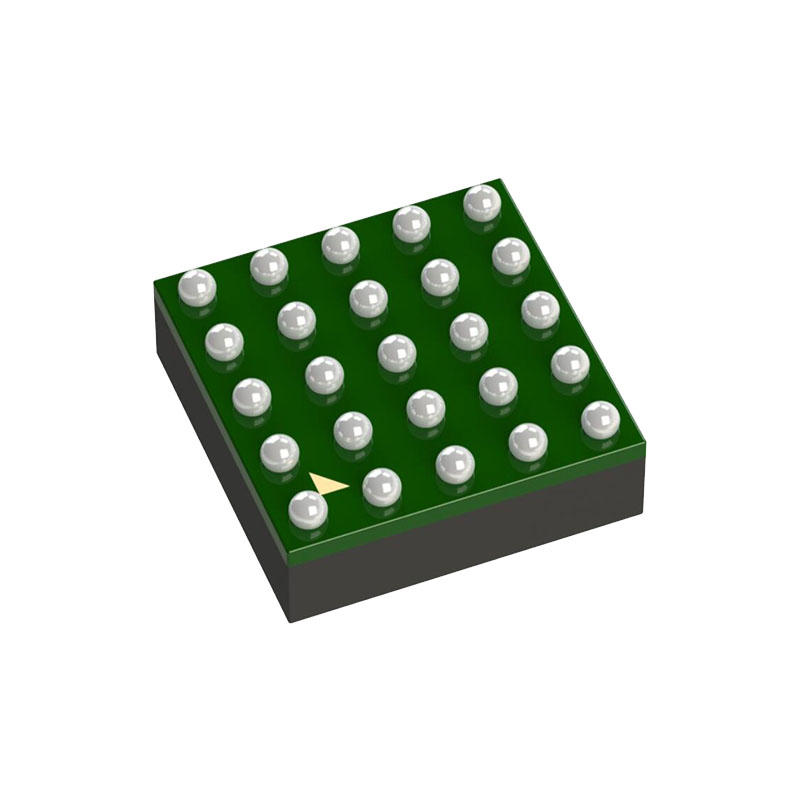

AD9634 - это 12-разрядный аналого-цифровой преобразователь (АЦП) со скоростью дискретизации до 250 MSPS. AD9634 предназначен для поддержки коммуникационных приложений, где требуется низкая стоимость, малые размеры, широкая полоса пропускания и универсальность. Ядро АЦП имеет многоступенчатую дифференциальную конвейерную архитектуру со встроенной логикой коррекции ошибок на выходе. АЦП оснащен широкополосными входами, которые могут поддерживать различные диапазоны входных сигналов, выбираемые пользователем. Встроенный источник опорного напряжения облегчает проектирование. Стабилизатор рабочего цикла (DCS) компенсирует колебания рабочего цикла АЦП, позволяя преобразователю сохранять отличные характеристики. Выходные данные АЦП направляются непосредственно во внешний 12-разрядный выходной порт LVDS. Гибкие возможности отключения питания позволяют значительно экономить электроэнергию, если это необходимо. Программирование для настройки и управления осуществляется с помощью 3-проводного последовательного интерфейса, совместимого с SPI. AD9634 выпускается в 32-выводном корпусе LFCSP и рассчитан на работу в промышленном диапазоне температур от -40°C до +85°C. Этот продукт защищен патентом США.

ОСНОВНЫЕ ХАРАКТЕРИСТИКИ ПРОДУКЦИИ

- Встроенный 12-битный, 170 MSPS/210 MSPS/250 MSPS АЦП.

- Быстрое определение превышения диапазона и порога.

- Собственный дифференциальный вход обеспечивает превосходные характеристики SNR для входных частот до 350 МГц.

- 3-контактный порт SPI с напряжением 1,8 В для программирования и считывания регистров.

- Совместимость с AD9642, обеспечивающая простой переход к 14 битам, и с AD6672.

ОСОБЕННОСТИ

SNR = 69,7 dBFS при AIN 185 МГц и 250 MSPS

SFDR = 87 дБк при частоте AIN 185 МГц и частоте 250 MSPS

Входной шум -150,6 дБФС/Гц при частоте 185 МГц, AIN -1 дБФС и частоте 250 MSPS

Общая потребляемая мощность: 360 мВт при 250 MSPS

Напряжение питания 1,8 В

Выходы LVDS (уровни ANSI-644)

Целочисленный делитель входного тактового генератора 1 к 8 (максимальная входная частота 625 МГц)

Частота дискретизации до 250 MSPS

Внутреннее опорное напряжение АЦП

Гибкий диапазон аналоговых входов от 1,4 В p-p до 2,0 В p-p (номинальный 1,75 В p-p)

Стабилизатор тактового цикла АЦП

Управление последовательным портом

Энергосберегающие режимы отключения питания

ПРИЛОЖЕНИЯ

Коммуникации

Радиосистемы разнесения

Многомодовые цифровые приемники (3G) TD-SCDMA, WiMAX, W-CDMA, CDMA2000, GSM, EDGE, LTE

Системы демодуляции I/Q

Интеллектуальные антенные системы

Программные радиостанции общего назначения

Ультразвуковое оборудование

Широкополосные приложения для передачи данных

ТЕОРИЯ ЭКСПЛУАТАЦИИ

The AD9634 can sample any fS/2 frequency segment from dc to 250 MHz using appropriate low-pass or band-pass filtering at the ADC inputs with little loss in ADC performance. Programming and control of the AD9634 are accomplished using a 3-pin, SPI-compatible serial interface.

ADC ARCHITECTURE

The AD9634 architecture consists of a front-end sample-andhold circuit, followed by a pipelined, switched-capacitor ADC. The quantized outputs from each stage are combined into a final 12-bit result in the digital correction logic. The pipelined architecture permits the first stage to operate on a new input sample and the remaining stages to operate on the preceding samples. Sampling occurs on the rising edge of the clock. Each stage of the pipeline, excluding the last, consists of a low resolution flash ADC connected to a switched-capacitor digitalto-analog converter (DAC) and an interstage residue amplifier (MDAC). The MDAC magnifies the difference between the reconstructed DAC output and the flash input for the next stage in the pipeline. One bit of redundancy is used in each stage to facilitate digital correction of flash errors. The last stage simply consists of a flash ADC. The input stage contains a differential sampling circuit that can be ac- or dc-coupled in differential or single-ended modes. The output staging block aligns the data, corrects errors, and passes the data to the output buffers. The output buffers are powered from a separate supply, allowing digital output noise to be separated from the analog core. During power-down, the output buffers go into a high impedance state.

For more parameters, please refer to the Datasheets.