ОБЩЕЕ ОПИСАНИЕ

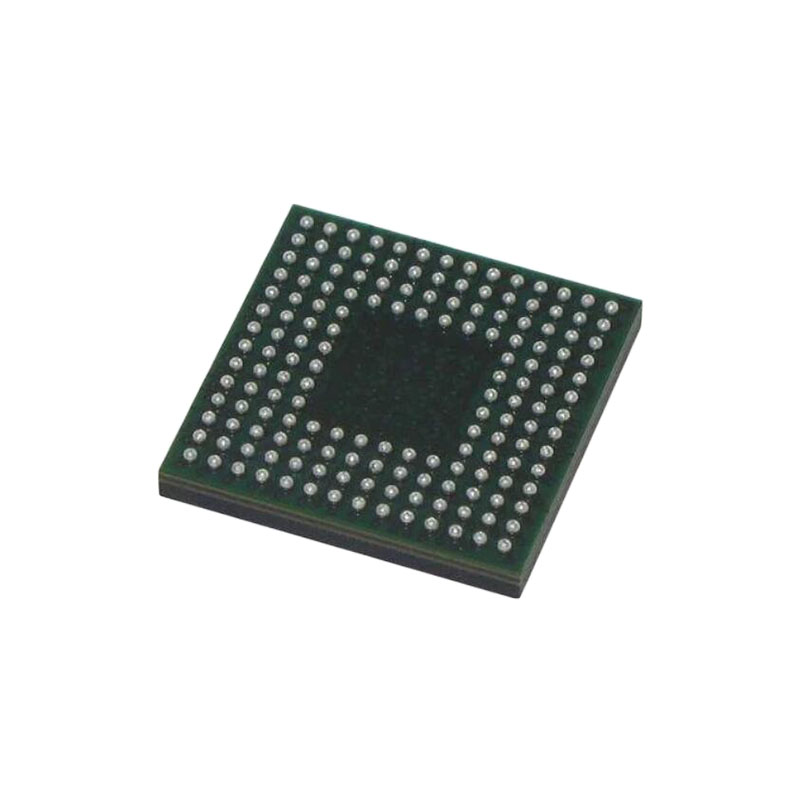

AD9736, AD9735 и AD9734 - это высокопроизводительные, высокочастотные ЦАП, обеспечивающие частоту дискретизации до 1200 MSPS и позволяющие генерировать многополосные сигналы вплоть до частоты Найквиста. AD9736 - 14-разрядный представитель семейства, а AD9735 и AD9734 - 12- и 10-разрядные представители, соответственно. Они оснащены портом последовательного периферийного интерфейса (SPI), который обеспечивает программирование многих внутренних параметров и позволяет считывать данные из регистров состояния. Для достижения высокой частоты дискретизации используется интерфейс LVDS уменьшенной спецификации. Выходной ток может быть запрограммирован в диапазоне от 8,66 мА до 31,66 мА. Микросхемы семейства AD973x изготавливаются по 0,18 мкм КМОП-технологии и работают от источников питания 1,8 В и 3,3 В при общей потребляемой мощности 380 мВт в режиме шунтирования. Микросхемы поставляются в 160-выводном корпусе с шариковой решеткой для уменьшения паразитных нагрузок на корпус.

ОСНОВНЫЕ ХАРАКТЕРИСТИКИ ПРОДУКЦИИ

1.Низкий уровень шума и интермодуляционных искажений (IMD) обеспечивает высокое качество синтеза широкополосных сигналов на промежуточных частотах до 600 МГц.

2.Приемники данных LVDS с двойной скоростью передачи данных (DDR) поддерживают максимальную скорость преобразования 1200 MSPS.

3.Прямое программирование основных функций или доступ к порту SPI обеспечивает полный контроль над всеми функциями семейства AD973x.

4.Изготовленные по КМОП-технологии, микросхемы семейства AD973x используют запатентованную технологию переключения, которая улучшает динамические характеристики.

5.Токовые выходы семейства AD9736 легко конфигурируются для топологий односторонних или дифференциальных цепей.

ОСОБЕННОСТИ

Семейство совместимых штырьков

Отличные динамические характеристики

AD9736: SFDR = 82 дБк при fOUT = 30 МГц

AD9736: SFDR = 69 дБк при fOUT = 130 МГц

AD9736: IMD = 87 дБк при fOUT = 30 МГц

AD9736: IMD = 82 дБк при fOUT = 130 МГц

Интерфейс данных LVDS с оконечными устройствами 100 Ω на кристалле

Встроенный самотестирование Целостность выборки LVDS Целостность передачи данных LVDS-ЦАП

Низкая мощность: 380 мВт (IFS = 20 мА; fOUT = 330 МГц)

Работа от двух источников питания 1,8/3,3 В

Регулируемый аналоговый выход 8,66 мА - 31,66 мА (RL = 25 Ω - 50 Ω)

Опорное напряжение 1,2 В на кристалле

160-выводной пакет с шариковой решеткой (CSP_BGA)

ПРИЛОЖЕНИЯ

Широкополосные системы связи Инфраструктура сотовой связи (цифровое предыскажение) Беспроводные CMTS/VOD "точка-точка

Приборы, автоматическое испытательное оборудование

Радар, авионика

ТЕОРИЯ ЭКСПЛУАТАЦИИ

AD9736, AD9735 и AD9734 - это 14-, 12- и 10-битные ЦАП, работающие с частотой обновления до 1,2 GSPS. Входные данные могут приниматься с полной частотой 1,2 GSPS, или может быть включен 2× интерполяционный фильтр (режим 2×), позволяющий работать с полной скоростью при частоте входных данных 600 MSPS. Входы DATA и DATACLK_IN - параллельные LVDS, соответствующие спецификациям IEEE LVDS с уменьшенным размахом, за исключением входного гистерезиса. Вход DATACLK_IN работает на половине скорости входного сигнала DATA в формате двойной скорости передачи данных (DDR). Входы DACCLK-/DACCLK+ (выводы E1 и F1) напрямую управляют ядром ЦАП, чтобы минимизировать джиттер тактового сигнала. Сигнал DACCLK также делится на 2 (режим 1× и 2×), а затем выводится как DATACLK_OUT.

Поддержание правильного совмещения данных и тактового генератора является общей проблемой для высокоскоростных ЦАП, осложняемой изменениями температуры и других условий эксплуатации. Использование сигнала DATACLK_OUT для генерации данных позволяет устранить большую часть внутренних изменений процесса, температуры и задержки напряжения. AD973x еще больше упрощает эту проблему высокоскоростного сбора данных благодаря двум адаптивным контроллерам синхронизации с замкнутым циклом. Один контроллер синхронизации управляет выравниванием данных LVDS и тактового генератора данных (контроллер LVDS), а другой управляет выравниванием данных LVDS и тактового генератора DACCLK (контроллер синхронизации). Контроллер LVDS определяет местоположение переходов данных и задерживает DATACLK_IN так, чтобы его переход находился в центре действующего окна данных. Контроллер синхронизации управляет FIFO, который перемещает данные из области LVDS DATACLK_IN в область DACCLK. Оба контроллера могут работать в ручном режиме под внешним управлением процессора, в режиме наблюдения, когда условия ошибки генерируют внешние прерывания, или в автоматическом режиме, когда ошибки автоматически исправляются. Контроллеры LVDS и синхронизации включают фильтрацию скользящего среднего для обеспечения помехоустойчивости и переменные пороги для контроля активности. Обычно контроллеры устанавливаются в автоматическом режиме, выполняя все необходимые настройки без пропусков или дублирования выборок на ЦАП. Перед переходом в режим автоматического обновления оба контроллера требуют первоначальной калибровки. Аналоговый выход AD973x изменяется через 35 тактов DACCLK после изменения входных данных в режиме 1× с отключенным FIFO. FIFO добавляет до восьми дополнительных циклов задержки. Эта задержка считывается из порта SPI. Колебания задержки внутреннего тактового генератора составляют менее одного цикла DACCLK на частоте 1,2 ГГц (833 пс). Остановка AD973x DATACLK_IN во время работы DACCLK может привести к непредсказуемым выходным сигналам. Это происходит потому, что внутренний тракт цифрового сигнала чередуется. Последние две выборки, поданные на ЦАП, продолжают подаваться на DACCLK даже после остановки DATACLK_IN. Результирующий выходной сигнал имеет частоту, равную половине fDAC, а его амплитуда зависит от разницы между двумя последними выборками. Управление функциями AD973x осуществляется через последовательно программируемые регистры, перечисленные в таблице 9. Кроме того, ограниченное число функций может быть напрямую задано внешними выводами в режиме pin.