ОБЩЕЕ ОПИСАНИЕ

The AD3542R is a low drift, dual channel, ultra-fast, 12-/16-bit accuracy, voltage output digital-to-analog converter (DAC) that can be configured in multiple voltage span ranges. The AD3542R operates with a fixed 2.5 V reference.

Каждый ЦАП включает три резистора обратной связи с компенсацией дрейфа для внутреннего трансимпедансного усилителя (TIA), который масштабирует выходное напряжение. Устройство имеет пять предварительно настроенных диапазонов выходного напряжения: от 0 В до 2,5 В, от 0 В до 5 В, от 0 В до 10 В, от -5 В до +5 В и от -2,5 В до +7,5 В.

The AD3542RBCPZ16 (hereafter referred to as AD3542R-16) can operate in fast mode for maximum speed or precision mode for maximum accuracy. The AD3542RBCPZ12 (hereafter referred to as AD3542R-12) has a single operation mode.

The serial peripheral interface (SPI) can be configured in dual synchronous SPI, dual SPI and single SPI (classic SPI) mode with single date rate (SDR) or double data rate (DDR), with logical levels from 1.2 V to 1.8 V.

The AD3542R is specified over the extended industrial temperature range (–40°C to +105°C).

ОСОБЕННОСТИ

12-/16-битное разрешение

Одноканальная скорость 16 MUPS в быстром режиме

11 MUPS скорость одного канала в точном режиме

Время установления малого сигнала 78 нс до точности 0,1%

Время установления большого сигнала 100 нс до точности 0,1%

Ультрамалый глюк: <50 pV×s

Сверхмалая задержка: 5 нс

THD: −105 dB at 1 kHz for AD3542R-16 and −95 dB at 1 kHz for AD3542R-12

5 выбираемых диапазонов выходного напряжения

Совместимость по логическому уровню 1,2 В и 1,8 В

Одиночный (классический) и двойной режимы SPI

Несколько детекторов ошибок, как аналоговых, так и цифровых

2,5 В внутреннего опорного напряжения, 10 ppm/°C максимум TC

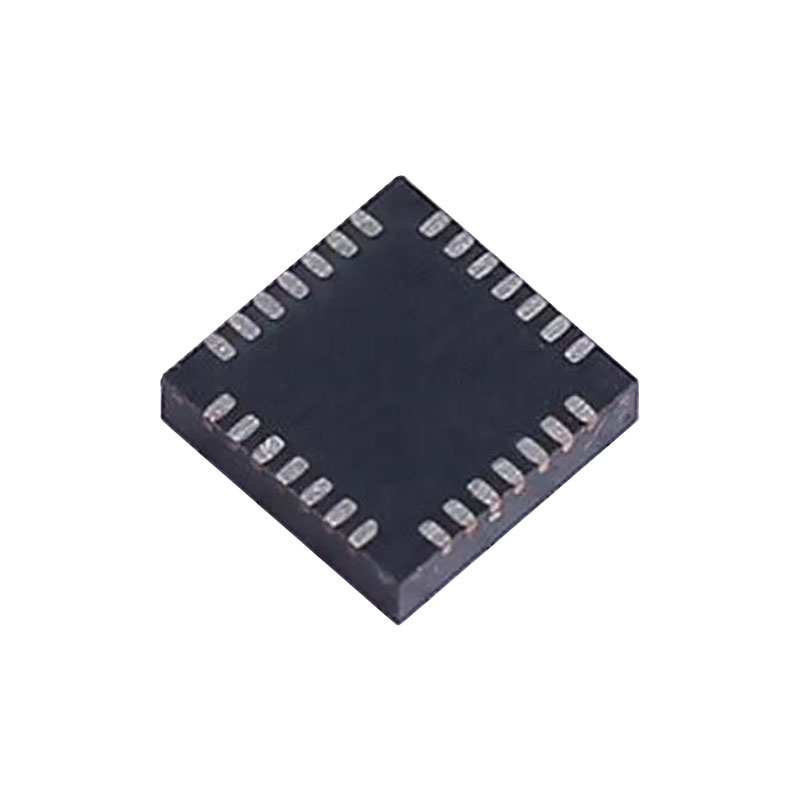

Малый корпус: 4 мм × 4 мм LFCSP

ПРИЛОЖЕНИЯ

Приборы

Аппаратное обеспечение в контуре

Оборудование для управления технологическими процессами

Медицинские приборы

Автоматизированное испытательное оборудование

Система сбора данных

Программируемые источники напряжения

Оптические коммуникации

ТЕОРИЯ ЭКСПЛУАТАЦИИ

Режим потоковой передачи

When the SINGLE_INSTRUCTION bit in the INTERFACE_CONFIG_ B register is set to 0, single instruction mode is disabled and streaming mode is enabled. In streaming mode, multiple registers with adjacent addresses can be accessed with a single instruction phase and data phase, allowing efficient access of contiguous regions of memory (for example, during initial device configuration). The AD3542R is configured in streaming mode by default.

В потоковом режиме каждый кадр SPI состоит из одной фазы команд, а следующая за ней фаза данных содержит данные для нескольких регистров со смежными адресами. Адрес начального регистра задается цифровым хостом в фазе команд, и этот адрес автоматически увеличивается или уменьшается (в зависимости от настройки направления адресации) после обращения к каждому байту данных. Поэтому фаза данных может иметь длину в несколько байт, и каждый следующий байт данных чтения или записи соответствует следующему старшему или младшему адресу регистра (для направления адресации по возрастанию и убыванию, соответственно).

При записи или чтении из многобайтового регистра в потоковом режиме с возрастанием адреса пользователь должен обратиться к младшему байту регистра в фазе команд. Фаза данных начинает передачу данных с младшего байта, стоящего на первом месте.

При записи или чтении из многобайтового регистра в потоковом режиме с убыванием адреса пользователь должен начать обращение к старшему байту регистра в фазе команд. Фаза данных начинает передавать старший байт первым.

ИНФОРМАЦИЯ О ПРИЛОЖЕНИЯХ

РЕКОМЕНДАЦИИ ПО ПИТАНИЮ

The AD3542R does not have any restriction for power supply sequencing. The chip incorporates a power monitor for AVDD and DVDD that releases the internal reset when both rails are within specification. Nevertheless, the recommended sequence to turn on the supply rails is GND, AVDD, DVDD, VLOGIC because it minimizes the power-up glitch. PVDD and PVSS are independent of the three previous supplies and can be switched on at any time. A small glitch (<100 mV) appears when PVDD reaches 2 V.

It is recommended to connect AGND and DGND together and have a single solid ground plane.

AVDD имеет постоянную потребляемую мощность, которая не зависит от частоты обновления. Главное предостережение для этой шины - обеспечить низкий уровень шума на высоких частотах, где AC PSRR ниже.

Потребляемая мощность DVDD зависит от частоты обновления и режима шины SPI. Динамический ток имеет быстрые колебания, которые приводят к шуму на шине. Если DVDD выводится из AVDD, рекомендуется использовать фильтр в дополнение к LDO, чтобы полностью устранить влияние на выход ЦАП.

VLOGIC has very low current demand that depends on the SPI bus mode and clock rate. Power consumption is maximum in readout operations in dual SPI mode.